- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369893 > MC10H641FN (MOTOROLA INC) SINGLE SUPPLY PECL-TTL 1:9 CLOCK DISTRIBUTION CHIP PDF資料下載

參數(shù)資料

| 型號: | MC10H641FN |

| 廠商: | MOTOROLA INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | SINGLE SUPPLY PECL-TTL 1:9 CLOCK DISTRIBUTION CHIP |

| 中文描述: | 10H SERIES, LOW SKEW CLOCK DRIVER, 9 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁數(shù): | 3/8頁 |

| 文件大小: | 115K |

| 代理商: | MC10H641FN |

MC10H641 MC100H641

2–3

MOTOROLA

MECL Data

DL122 — Rev 6

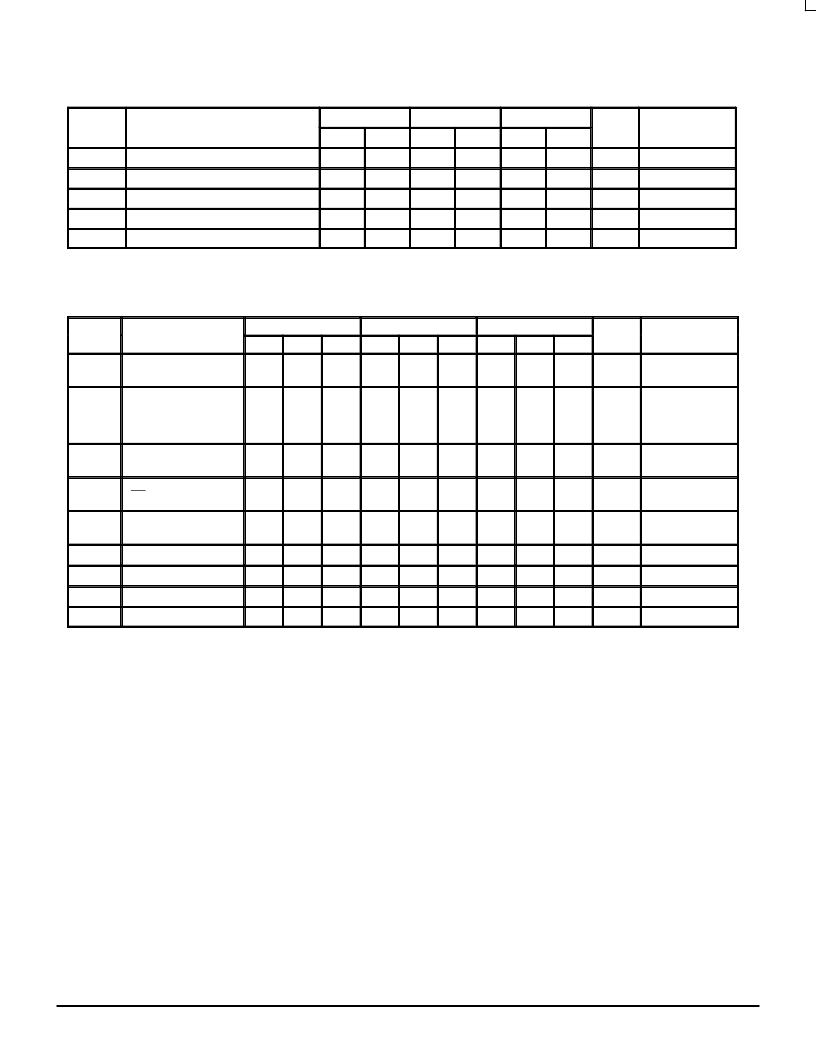

100H PECL DC CHARACTERISTICS

0

°

C

25

°

C

85

°

C

Symbol

Characteristic

Min

Max

Min

Max

Min

Max

Unit

Condition

IIH

IIL

VIH

VIL

VBB

1. PECL VIH, VIL, and VBB are referenced to VE and will vary 1:1 with the power supply. The levels shown are for VE = 5.0V.

Input HIGH Curren

225

175

175

μ

A

Input LOW Current

0.5

0.5

0.5

μ

A

Input HIGH Voltage

3.835

4.120

3.835

4.120

3.835

4.120

V

VE = 5.0V

1

VE = 5.0V

1

VE = 5.0V

1

Input LOW Voltage

3.190

3.525

3.190

3.525

3.190

3.525

V

Output Reference Voltage

3.62

3.74

3.62

3.74

3.62

3.74

V

AC CHARACTERISTICS

(VT = VE = 5.0V

±

5%)

TJ = 0

°

C

Typ

TJ = + 25

°

C

Typ

TJ = + 85

°

C

Typ

Symbol

Characteristic

Min

Max

Min

Max

Min

Max

Unit

Condition

CL = 50 pF

1

tPLH

tPHL

Propagation Delay

D to Q

5.00

5.36

5.50

5.86

6.00

6.36

4.86

5.27

5.36

5.77

5.86

6.27

5.08

5.43

5.58

5.93

6.08

6.43

ns

tskew

Device Skew

Part–to–Part

Single VCC

Output–to–Output

1000

750

350

1000

750

350

1000

750

350

ps

CL = 50pF

2

CL = 50 pF

3

CL = 50 pF

4

tPLH

tPHL

Propagation Delay

LEN to Q

4.9

6.9

4.9

6.9

5.0

7.0

ns

CL = 50 pF

tPLH

tPHL

Propagation Delay

EN to Q

5.0

7.0

4.9

6.9

5.0

7.0

ns

CL = 50 pF

tr

tf

Output Rise/Fall

0.8V to 2.0V

1.7

1.6

1.7

1.6

1.7

1.6

ns

CL = 50 pF

fMAX

Max Input Frequency

65

65

65

MHz

CL = 50 pF

5

tREC

Recovery Time EN

1.25

1.25

1.25

ns

tS

Setup Time

0.75

0.50

0.75

0.50

0.75

0.50

ns

tH

Hold Time

0.75

0.50

0.75

0.50

0.75

0.50

ns

1. Propagation delay measurement guaranteed for junction temperatures. Measurements performed at 50MHz input frequency.

2. Skew window guaranteed for a single temperature across a VCC = VT = VE of 4.75V to 5.25V (See Application Note in this datasheet).

3. Skew window guaranteed for a single temperature and single VCC = VT = VE

4. Output–to–output skew is specified for identical transitions through the device.

5. Frequency at which output levels will meet a 0.8V to 2.0V minimum swing.

DETERMINING SKEW FOR A SPECIFIC APPLICATION

The H641 has been designed to meet the needs of very low

skew clock distribution applications. In order to optimize the

device for this application special considerations are

necessary in the determining of the part–to–part skew

specification limits. Older standard logic devices are specified

with relatively slack limits so that the device can be

guaranteed over a wide range of potential environmental

conditions. This range of conditions represented all of the

potential applications in which the device could be used. The

result was a specification limit that in the vast majority of cases

was extremely conservative and thus did not allow for an

optimum system design. For non–critical skew designs this

practice is acceptable, however as the clock speeds of

systems increase overly conservative specification limits can

kill a design.

The following will discuss how users can use the

information provided in this data sheet to tailor a part–to–part

skew specification limit to their application. The skew

determination process may appear somewhat tedious and

time consuming, however if the utmost in performance is

required this procedure is necessary. For applications which

do not require this level of skew performance a generic

part–to–part skew limit of 2.5ns can be used. This limit is good

for the entire ambient temperature range, the guaranteed VCC

(VT, VE) range and the guaranteed operating frequency range.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC10170L | 9+2-Bit Parity Generator/Checker |

| MC10170 | 9+2-Bit Parity Generator/Checker |

| MC10170P | 9+2-Bit Parity Generator/Checker |

| MC10171L | Dual Binary to 1-4 Decoder(Low) |

| MC10171 | Dual Binary to 1-4 Decoder(Low) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC10H641FNG | 功能描述:轉(zhuǎn)換 - 電壓電平 5V PECL to TTL 1:9 Clock Driver RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| MC10H641FNR2 | 功能描述:轉(zhuǎn)換 - 電壓電平 5V PECL to TTL 1:9 RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| MC10H641FNR2G | 功能描述:轉(zhuǎn)換 - 電壓電平 5V PECL to TTL 1:9 Clock Driver RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| MC10H642 C57M WAF | 制造商:ON Semiconductor 功能描述: |

| MC10H642FN | 功能描述:時鐘驅(qū)動器及分配 ECL/TTL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。