- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369893 > MC10170 (Motorola, Inc.) 9+2-Bit Parity Generator/Checker PDF資料下載

參數(shù)資料

| 型號: | MC10170 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 9+2-Bit Parity Generator/Checker |

| 中文描述: | 9 2位奇偶發(fā)生器/檢查 |

| 文件頁數(shù): | 1/4頁 |

| 文件大小: | 81K |

| 代理商: | MC10170 |

SEMICONDUCTOR TECHNICAL DATA

3–103

REV 6

Motorola, Inc. 1996

9/96

The MC10170 is a 11–bit parity circuit, which is segmented into 9 data bits

and 2 control bits.

Output A generates odd parity on 9 bits; that is, Output A goes high for an

odd number of high logic levels on the bit inputs in only 2 gate delays.

The Control Inputs can be used to expand parity to larger numbers of bits

with minimal delay or can be used to generate even parity. To expand parity to

larger words, the MC10170 can be used with the MC10160 or other

MC10170’s. The MC10170 can generate both even and odd parity.

PD= 300 mW typ/pkg (No Load)

tpd= 2.5 ns typ(Control Inputs to B Output)

4.0 ns typ (Data Inputs to A Output)

6.0 ns typ (Data Inputs to B Output)

tr,tf= 2.0 ns typ (20%–80%)

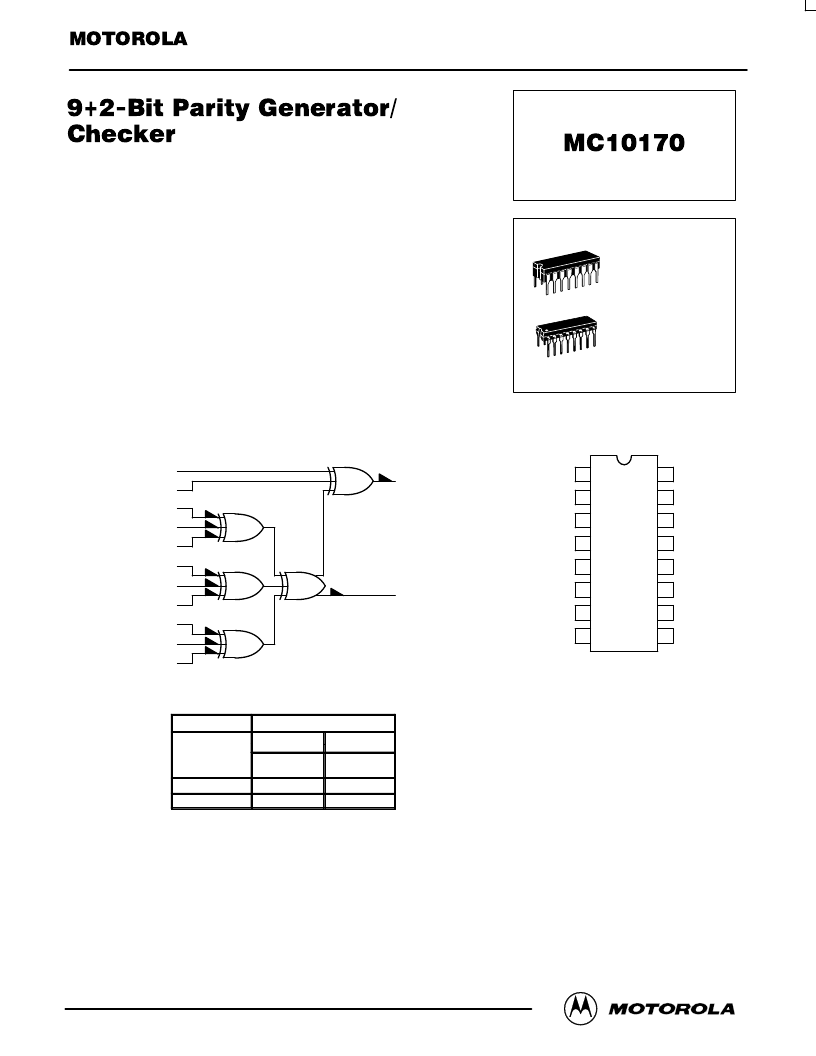

LOGIC DIAGRAM

VCC1= PIN 1

VCC2= PIN 16

VEE= PIN 8

2 A

ODD PARITY

15 B

EVEN PARITY

13 HIGH

14 LOW

3

D0

4

D1

5

D2

6

D3

7

D4

9

D5

10

D6

11

D7

12

D8

CONTROL

INPUTS

INPUTS

OUTPUTS

Sum of

D Inp ts

D Inputs

at High Level

Even

Odd

Odd Parity

Even Parity

Output A

Output B

Low

High

High

Low

PIN ASSIGNMENT

VCC1

A

D0

D1

D2

D3

D4

VEE

VCC2

B

LOW

HIGH

D8

D7

D6

D5

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

L SUFFIX

CERAMIC PACKAGE

CASE 620–10

P SUFFIX

PLASTIC PACKAGE

CASE 648–08

相關PDF資料 |

PDF描述 |

|---|---|

| MC10170P | 9+2-Bit Parity Generator/Checker |

| MC10171L | Dual Binary to 1-4 Decoder(Low) |

| MC10171 | Dual Binary to 1-4 Decoder(Low) |

| MC10171P | Dual Binary to 1-4 Decoder(Low) |

| MC10171FN | Dual Binary to 1-4 Decoder(Low) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC10170L | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC10170P | 制造商:Motorola Inc 功能描述: |

| MC10171FN WAF | 制造商:ON Semiconductor 功能描述: |

| MC10171L | 制造商:ON Semiconductor 功能描述:Decoder/Demultiplexer Dual 2-to-4 16-Pin CDIP Rail |

| MC10171P | 制造商:ON Semiconductor 功能描述:Decoder/Demultiplexer Dual 2-to-4 16-Pin PDIP Rail 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。