- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377885 > MB814265-60 (Fujitsu Limited) CMOS 256K ×16 BIT Hyper Page Mode Dynamic RAM(CMOS 256K ×16 位超級(jí)頁(yè)面存取模式動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | MB814265-60 |

| 廠商: | Fujitsu Limited |

| 英文描述: | CMOS 256K ×16 BIT Hyper Page Mode Dynamic RAM(CMOS 256K ×16 位超級(jí)頁(yè)面存取模式動(dòng)態(tài)RAM) |

| 中文描述: | 的CMOS 256K × 16位的超頁(yè)模式動(dòng)態(tài)RAM的CMOS(256K × 16位超級(jí)頁(yè)面存取模式動(dòng)態(tài)內(nèi)存) |

| 文件頁(yè)數(shù): | 25/28頁(yè) |

| 文件大小: | 364K |

| 代理商: | MB814265-60 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

25

MB814265-60/MB814265-70

DESCRIPTION

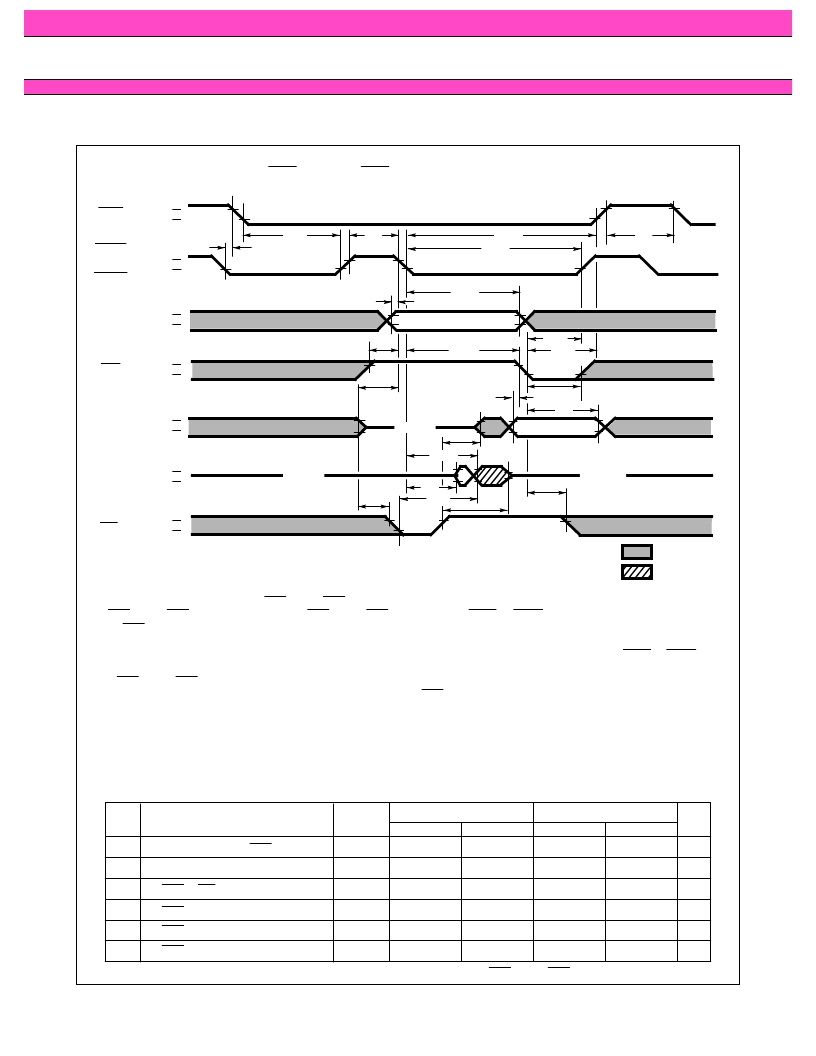

A special timing sequence using the CAS-before-RAS refresh counter test cycle provides a convenient method to verify the functionality

of CAS-before-RAS refresh circuitry. After a CAS-before-RAS refresh cycle, if LCAS or UCAS makes a transition from High to Low

while RAS is held Low, read and write operations are enabled as shown above. Row and column addresses are defined as follows:

Row Address: Bits A

0

through A

8

are defined by the on-chip refresh counter.

Column Address: Bits A

0

through A

8

are defined by latching levels on A

0

-A

8

at the second falling edge of LCAS or UCAS.

The CAS-before-RAS Counter Test procedure is as follows ;

1) Normalize the internal refresh address counter by using 8 RAS-only refresh cycles.

2) Use the same column address throughout the test.

3) Write “0” to all 512 row addresses at the same column address by using CBR refresh counter test cycles.

4) Read “0” written in procedure 3) by using normal read cycle and check; After reading ”0” and check are completed

(or simultaneously), write “1” to the same addresses by using normal write cycle (or read-modify-write cycle).

5) Read and check data “1” written in procedure 4) by using CBR refresh counter test cycle for all 512 memory locations.

6) Reverse test data and repeat procedures 3), 4), and 5).

Fig. 19 – CAS-BEFORE-RAS REFRESH COUNTER TEST CYCLE

DQ

(Input)

DQ

(Output)

RAS

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

V

IH

V

IL

LCAS

or

UCAS

WE

A

0

to A

8

V

OH

V

OL

V

IH

V

IL

OE

(At recommended operating conditions unless otherwise noted.)

Note: Assumes that CAS-before-RAS refresh counter test cycle only.

t

CSR

“H” or ”L”

Valid Data

t

RP

t

CP

t

RCS

t

FCAH

t

ASC

t

WP

t

CHR

t

FRSH

t

FCWD

t

DH

t

DS

t

DZC

t

OED

t

ON

t

OEA

t

DZO

t

OEZ

t

OEH

VALID DATA IN

COLUMN ADDRESSES

t

FCAC

HIGH-Z

HIGH-Z

t

FCAS

HIGH-Z

t

CWL

t

RWL

Parameter

Unit

Min.

Max.

No.

Min.

Max.

90

55

Symbol

91

30

—

—

30

92

80

80

55

—

—

μ

s

ns

ns

Access Time from CAS

Column Adress Hold Time

CAS to WE Delay Time

93

—

55

55

94

55

—

—

55

—

μ

s

ns

CAS Pulse Width

RAS Hold Time

95

85

—

—

85

ns

CAS Hold Time

—

—

MB814265-60

MB814265-70

t

FCAC

t

FCAH

t

FCWD

t

FCAS

t

FRSH

t

FCSH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB814265-70 | CMOS 256K ×16 BIT Hyper Page Mode Dynamic RAM(CMOS 256K ×16 位超級(jí)頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400A-60 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400A-70 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400A-80 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400C-60 | CMOS 1 M ×4BIT Fast Page Mode DRAM(CMOS 1 M ×4 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB814400C-70PJN | 制造商:FUJITSU 功能描述:Dynamic RAM, Fast Page, 1M x 4, 26 Pin, Plastic, SOJ |

| MB814405D-60PJN | 制造商:FUJITSU Component Ltd 功能描述: |

| MB8146112 | 制造商:FUJITSU 功能描述:* |

| MB81461-12PSZ | 制造商:FUJITSU 功能描述:VRAM, FAST PAGE, 64KX4, 24 Pin, Plastic, ZIP |

| MB81461B-12 | 制造商:FUJITSU 功能描述: 制造商:FUGITSU 功能描述:81461B-12 制造商:FUJITSU 功能描述:81461B-12 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。