- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄11564 > MAX3421EETJ+T (Maxim Integrated Products)IC USB PERIPH/HOST CNTRL 32TQFN PDF資料下載

參數(shù)資料

| 型號: | MAX3421EETJ+T |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 7/28頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC USB PERIPH/HOST CNTRL 32TQFN |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 2,500 |

| 控制器類型: | USB 外設(shè)控制器 |

| 接口: | USB/串行 |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 15mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-WFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 32-TQFN-EP(5x5) |

| 包裝: | 帶卷 (TR) |

| 配用: | MAX3421EVKIT-1+-ND - EVAL KIT FOR MAX3421E |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

MAX3421E

USB Peripheral/Host Controller

with SPI Interface

15

Maxim Integrated

Typical Operating Characteristics

(VCC = +3.3V, VL = +3.3V, TA = +25°C.)

Detailed Description

The MAX3421E contains digital logic and analog cir-

cuitry necessary to implement a full-speed USB periph-

eral or a full-/low-speed host compliant to USB

specification rev 2.0. The MAX3421E is selected to

operate as either a host or peripheral by writing to the

HOST bit in the MODE (R27) register. The MAX3421E

features an internal USB transceiver with ±15kV ESD

protection on D+, D-, and VBCOMP. A switchable

1.5k

Ω pullup resistor is provided on D+ and switchable

15k

Ω pulldown resistors are provided on both D+ and

D-. Any SPI master can communicate with the

MAX3421E through the SPI slave interface that oper-

ates in SPI mode (0,0) or (1,1). An SPI master accesses

the MAX3421E by reading and writing to internal regis-

ters. A typical data transfer consists of writing a first

byte that sets a register address and direction with

additional bytes reading or writing data to the register

or internal FIFO.

In peripheral mode, the MAX3421E contains 384 bytes

of endpoint buffer memory, implementing the following

endpoints:

EP0: 64-byte bidirectional CONTROL endpoint

EP1: 2 x 64-byte double-buffered BULK/INT

OUT endpoint

EP2: 2 x 64-byte double-buffered BULK/INT IN

endpoint

EP3: 64-byte BULK/INT IN endpoint

The choice to use EP1, EP2, EP3 as BULK or INTER-

RUPT endpoints is strictly a function of the endpoint

descriptors that the SPI master returns to the USB host

during enumeration.

In host mode, the MAX3421E contains 256 bytes of

send and receive FIFO memory:

SNDFIFO: Send FIFO—double-buffered 64-byte

FIFO

RCVFIFO: Receive FIFO—double-buffered 64-byte

FIFO

The host FIFOs can send SETUP, BULK, INTERRUPT,

and ISOCHRONOUS requests to a peripheral device, at

full speed or low speed. The MAX3421E accommodates

low-speed devices whether they are directly connected,

or connected through a USB hub. Because the

MAX3421E does much of the host housekeeping, it is

easy to program. The SPI master does a typical host

operation by setting the device address and endpoint,

launching a packet, and waiting for a completion inter-

rupt. Then it examines transfer result bits to determine

how the peripheral responded. It automatically gener-

ates frame markers (full-speed SOF packets or low-

speed keep-alive pulses), and ensures that packets are

dispatched at the correct times relative to these markers.

The MAX3421E register set and SPI interface is optimized

to reduce SPI traffic. An interrupt output pin, INT, notifies

the SPI master when USB service is required; for exam-

ple, when a packet arrives, a packet is sent, or the host

suspends or resumes bus activity. Double-buffered FIFOs

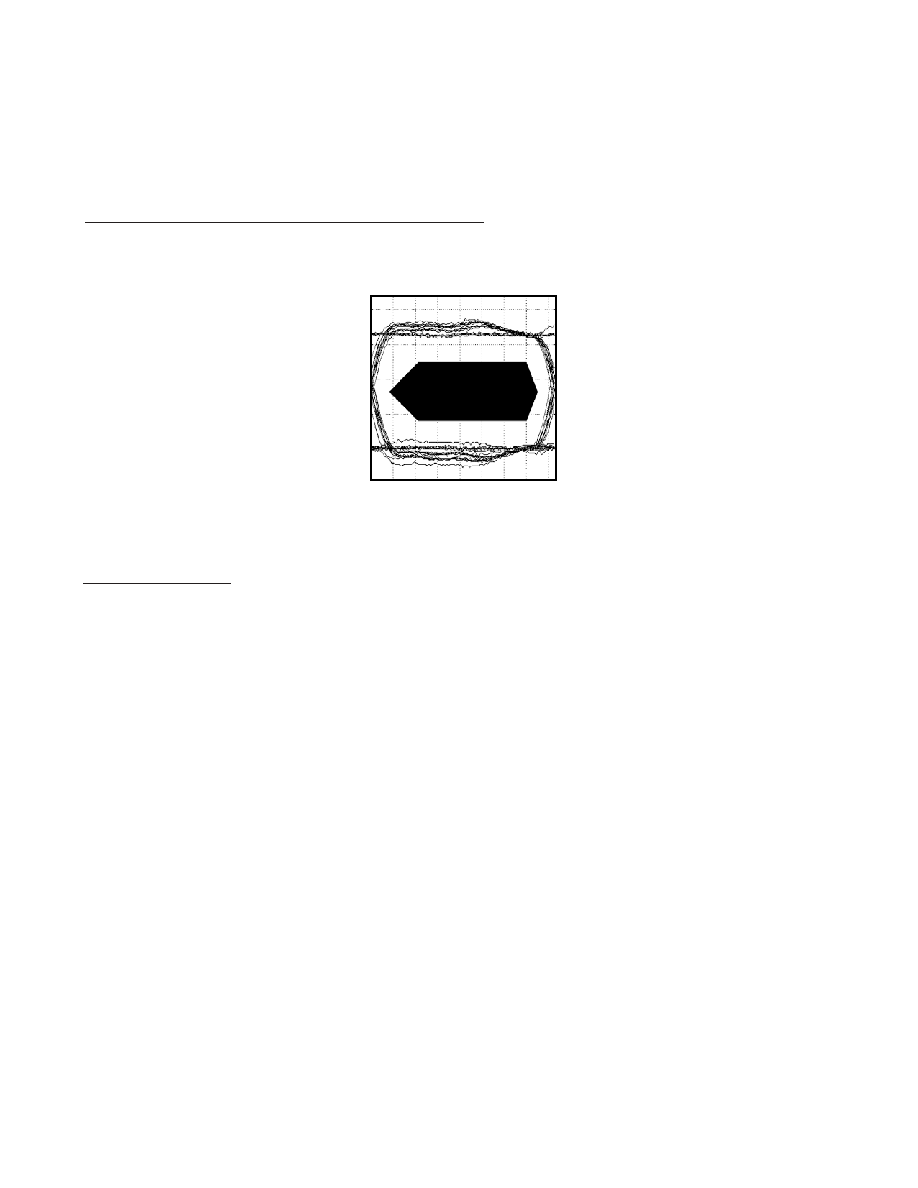

EYE DIAGRAM

MAX3421E

toc01

4

1

0

-1

0

1020304050607080

2

3

TIME (ns)

D+

AND

D-

(V)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V375C28M75B3 | CONVERTER MOD DC/DC 28V 75W |

| MAX5942BESE+ | IC IEEE 802.3AF POE SYSTM 16SOIC |

| 78Q8430-100IGTR/F | IC LAN MEDIA ACCESS CTLR 100LQFP |

| GRM2165C1H510JZ01D | CAP CER 51PF 50V 5% NP0 0805 |

| MAX5942BCSE+ | IC IEEE 802.3AF POE SYSTM 16SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3421EVKIT-1+ | 功能描述:界面開發(fā)工具 MAX3421E/20E Eval Kit RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| MAX3430CPA | 功能描述:RS-485接口IC RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:250 Kbps 工作電源電壓:3.3 V 電源電流:750 uA 工作溫度范圍:- 40 C to + 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

| MAX3430CPA+ | 功能描述:RS-485接口IC Fail-Safe 1/4-Unit 3.3V Transceiver RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:250 Kbps 工作電源電壓:3.3 V 電源電流:750 uA 工作溫度范圍:- 40 C to + 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

| MAX3430CSA | 功能描述:RS-485接口IC RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:250 Kbps 工作電源電壓:3.3 V 電源電流:750 uA 工作溫度范圍:- 40 C to + 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

| MAX3430CSA+ | 功能描述:RS-485接口IC Fail-Safe 1/4-Unit 3.3V Transceiver RoHS:否 制造商:Texas Instruments 數(shù)據(jù)速率:250 Kbps 工作電源電壓:3.3 V 電源電流:750 uA 工作溫度范圍:- 40 C to + 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。