- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄180472 > MACH131SP-7VC (LATTICE SEMICONDUCTOR CORP) High-Performance EE CMOS Programmable Logic PDF資料下載

參數(shù)資料

| 型號(hào): | MACH131SP-7VC |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類(lèi): | PLD |

| 英文描述: | High-Performance EE CMOS Programmable Logic |

| 中文描述: | EE PLD, 7.5 ns, PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁(yè)數(shù): | 46/48頁(yè) |

| 文件大小: | 1136K |

| 代理商: | MACH131SP-7VC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)第47頁(yè)第48頁(yè)

MACH 1 & 2 Families

7

Macrocell

There are two fundamental types of macrocell: the output macrocell and the buried macrocell. The

buried macrocell is only found in MACH 2 devices. The use of buried macrocells effectively

doubles the number of macrocells available without increasing the pin count.

Both macrocell types can generate registered or combinatorial outputs. For the MACH 2 series,

a transparent-low latch conguration is provided. If the register is used, it can be congured as

a T-type or a D-type ip-op. Register and latch functionality is dened in Table 9.

Programmable polarity (for output macrocells) and the T-type ip-op both give the software a

way to minimize the number of product terms needed. These choices can be made automatically

by the software when it ts the design into the device.

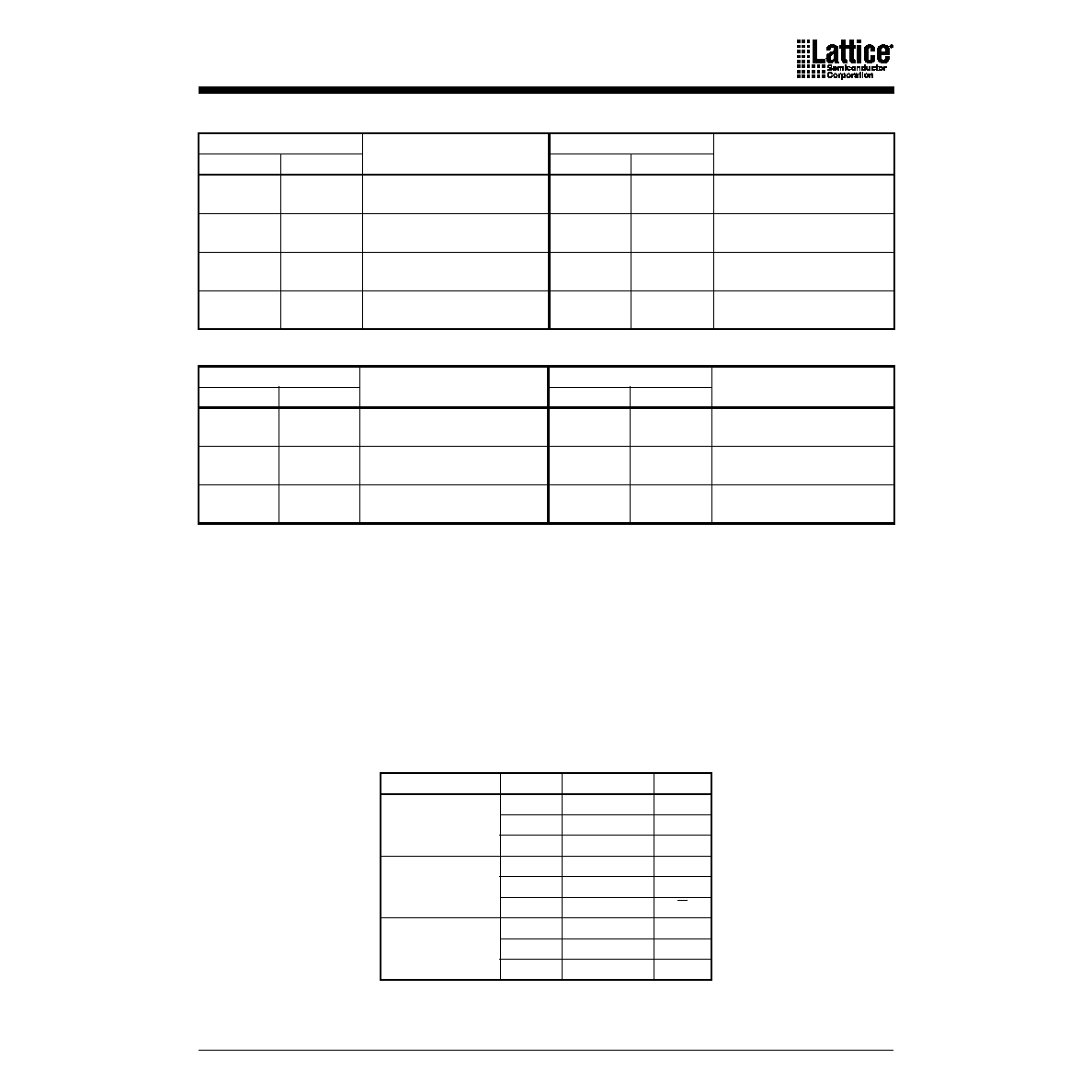

Table 7. Logic Allocation for MACH211(SP) and MACH231(SP)

Macrocell

Available Clusters

Macrocell

Available Clusters

Output

Buried

Output

Buried

M0

M1

C0, C1, C2

C0, C1, C2, C3

M8

M9

C7, C8, C9, C10

C8, C9, C10, C11

M2

M3

C1, C2, C3, C4

C2, C3, C4, C5

M10

M11

C9, C10, C11, C12

C10, C11, C12, C13

M4

M5

C3, C4, C5, C6

C4, C5, C6, C7

M12

M13

C11, C12, C13, C14

C12, C13, C14, C15

M6

M7

C5, C6, C7, C8

C6, C7, C8, C9

M14

M15

C13, C14, C15

C14, C15

Table 8. Logic Allocation for MACH221(SP)

Macrocell

Available Clusters

Macrocell

Available Clusters

Output

Buried

Output

Buried

M0

M1

C0, C1, C2

C0, C1, C2, C3

M6

M7

C5, C6, C7, C8

C6, C7, C8, C9

M2

M3

C1, C2, C3, C4

C2, C3, C4, C5

M8

M9

C7, C8, C9, C10

C8, C9, C10, C11

M4

M5

C3, C4, C5, C6

C4, C5, C6, C7

M10

M11

C9, C10, C11

C10, C11

Table 9. Register/Latch Operation

Conguration

D/T

CLK/LE

Q+

D-Register

X

0,1,

↓

Q

0

↑

0

1

↑

1

T-Register

X

0,1,

↓

Q

0

↑

Q

1

↑

Q

Latch

X1

Q

00

0

10

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MACH131SP-7YI | High-Performance EE CMOS Programmable Logic |

| MACH120-12JC | High-Performance EE CMOS Programmable Logic |

| MACH120-15JC | High-Performance EE CMOS Programmable Logic |

| MACH120-12 | High-Performance EE CMOS Programmable Logic |

| MACH131SP-12YC | High-Performance EE CMOS Programmable Logic |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MACH131SP-7YC | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH131SP-7YI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 HI PERF EE CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| MACH210 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:44 pin QFP socket/28 pin DIP 0.6” plug |

| MACH210-12 | 制造商:AMD 制造商全稱(chēng):Advanced Micro Devices 功能描述:High-Density EE CMOS Programmable Logic |

| MACH21012JC | 制造商:AMD 功能描述:* |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。