- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370973 > M5M4V16G50DFP-12 (Mitsubishi Electric Corporation) 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM PDF資料下載

參數(shù)資料

| 型號(hào): | M5M4V16G50DFP-12 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| 中文描述: | 1,600(2 -銀行甲262144字× 32位)同步圖形RAM |

| 文件頁(yè)數(shù): | 21/33頁(yè) |

| 文件大小: | 167K |

| 代理商: | M5M4V16G50DFP-12 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)

M5M4V16G50DFP -8, -10, -12

Jan'97

Preliminary

MITSUBISHI LSIs

16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM

MITSUBISHI ELECTRIC

SGRAM (Rev. 0.0)

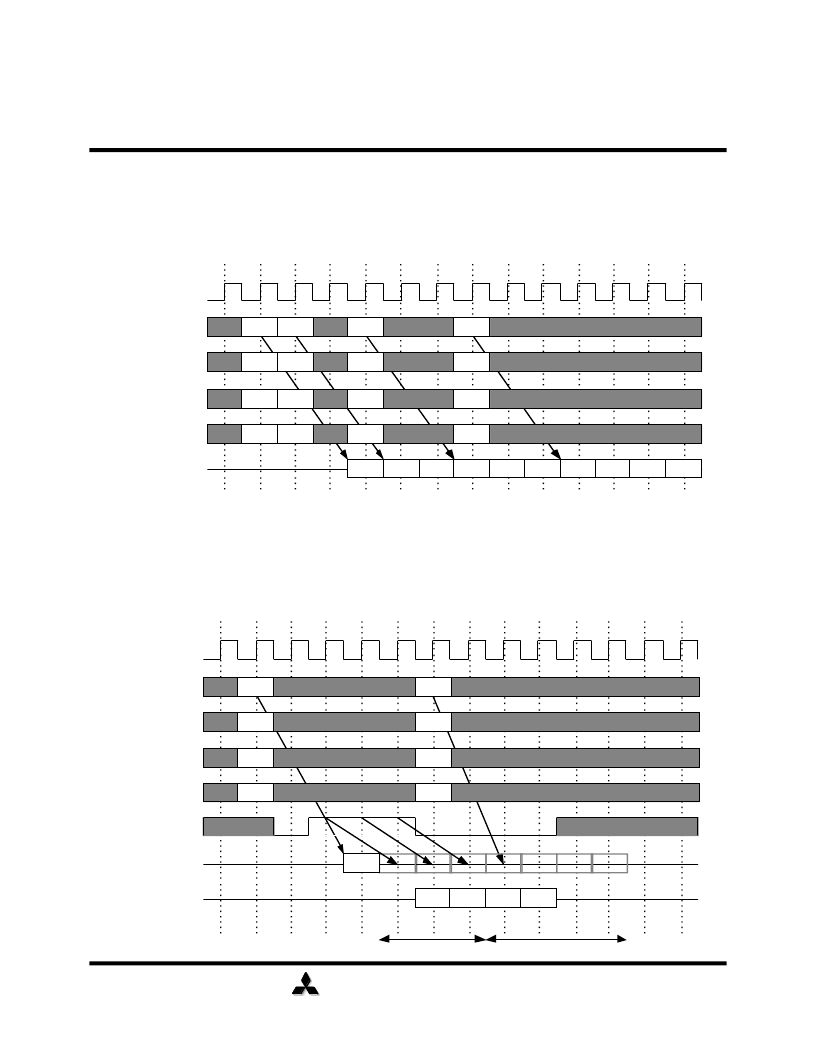

BURST INTERRUPTION

[ Read Interrupted by Read ]

Burst read operation can be interrupted by new read of the same or the other bank. M5M4V16G50DFP

allows random column access. READ to READ interval is minimum 1 CLK.

[ Read Interrupted by Write ]

Burst read operation can be interrupted by write of the same or the other bank. Random column access is

allowed. In this case, the DQ should be controlled adequately by using the DQM0 - 3 to prevent

bus contention. The output is disabled automatically 2 cycles after WRITE assertion.

Read Interrupted by Read (BL=4, CL=3)

CLK

Command

A0-8

A9

A10

DQ

READ

Yi

0

0

READ

Yk

0

1

Qai0

Qaj1 Qbk0 Qbk1

READ

Yj

0

0

Qaj0

Qbk2

Qal0

READ

Yl

0

0

Qal1

Qal2

Qal3

Read Interrupted by Write (BL=4, CL=3)

CLK

Command

A0-8

A9

A10

Q

READ

Yi

0

0

Qai0

Write

Yj

0

0

D

Daj0

Daj1

Daj2

Daj3

DQM0-3

DQM0-3

control

Write control

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V16G50DFP-8 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| M5M4V64S20ATP-10 | 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10L | 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-12 | 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-8 | 64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V16G50DFP-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| M5M4V17400CTP-60 | 制造商:Mitsubishi Electric 功能描述: |

| M5M4V18165CJ-7S | 制造商:MITSUBI 功能描述:Electronic Component |

| M5M4V4169TP20 | 制造商:MITSU 功能描述: |

| M5M4V4265CJ | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE) MODE 4194304-BIT (262144-WORD BY 16-BIT) DYNAMIC RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。