- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370973 > M5M4V16169DRT-15 (Mitsubishi Electric Corporation) 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M5M4V16169DRT-15 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| 中文描述: | 16MCDRAM:16米(100萬字由16位)與16K的緩存內(nèi)存(1024字由16位)的SRAM |

| 文件頁(yè)數(shù): | 10/64頁(yè) |

| 文件大?。?/td> | 737K |

| 代理商: | M5M4V16169DRT-15 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

M5M4V16169DTP/RT-7,-8,-10,-15

16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM

MODE DESCRIPTIONS (3)

MITSUBISHI LSIs

(REV 1.0) Jul. 1998

MITSUBISHI ELECTRIC

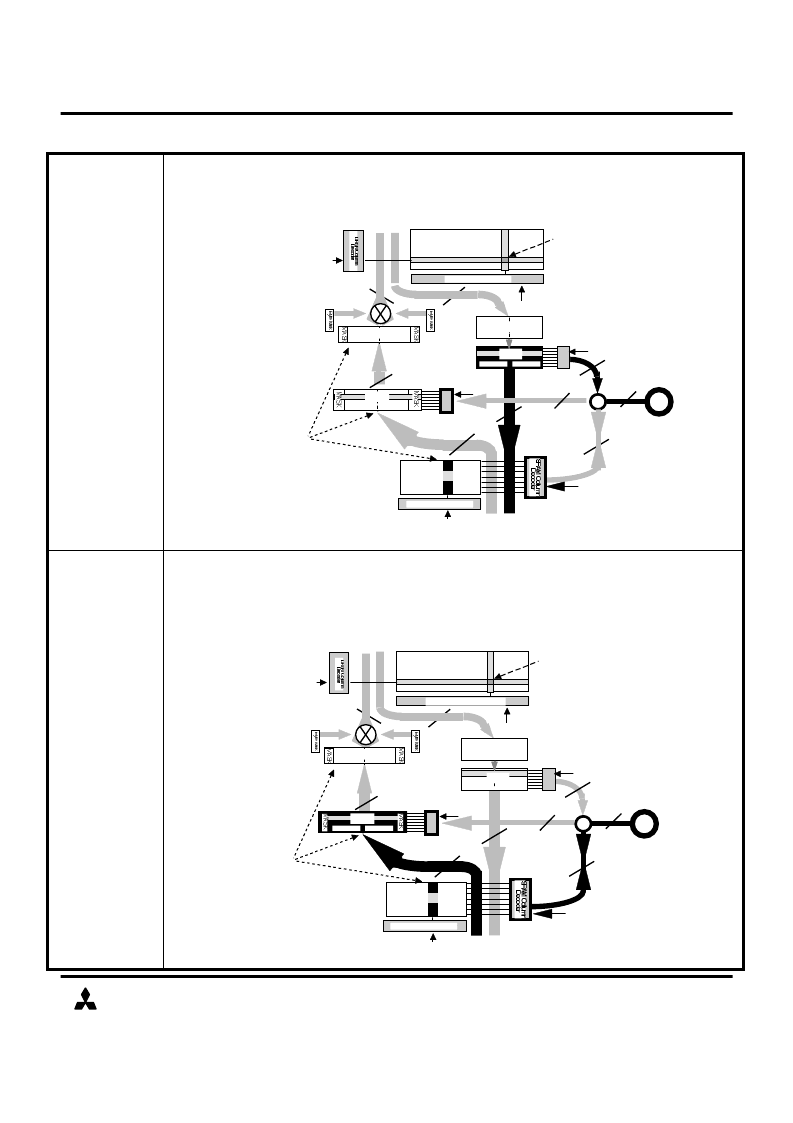

Buffer Read

Transfer &

SRAM Read

Buffer Write

Transfer &

SRAM Write

Data is transferred from the Read Buffer (RB2) to the SRAM, and simultaneously, data (16

bit word) is read from the RB2 to the I/O pins. Addresses As3-9 select the SRAM Row to

which the 8X16 bit block is to be written. Addresses As0-As2 decode the 16-bit word to be

read.

Data is first written from the I/O pins to SRAM as decoded by As0-As9. Then, the SRAM

Row (=Block) decoded by As3-As9 is transferred to the Write-Buffer1 (WB1). The Buffer

Write Transfer cycle "clears" all transfer mask bits in the WB1 Mask (allowing all data to be

transferred in a successive DRAM Write Transfer cycle). DQCu and DQCl control Upper

and Lower byte writes respectively, however all transfer mask bits in the WB1 are cleared.

10

X

DQs

SRAM

1KX16

8X16

8X16

8X16

8X16

8X16

16bits

16bits

16bits

As3-9

1of128Decode

SRAM RowDecoder

DRAM

1M X 16

Ad0-11

1of4096Decode

Ad3-7

1of32

Decode

As0-2

As0-2

1of8Decode

8X16Block

8X16Block

WB1

Upper Byte

Lower Byte

Upper Byte

Lower Byte

DRAM RowDecoder

16bits

As0-2

1of8Decode

Upper Byte

Lower Byte

Upper Byte

Lower Byte

X

DQs

SRAM

1KX16

8X16

8X16

8X16

8X16

8X16

16bits

16bits

16bits

As3-9

1of128Decode

SRAM RowDecoder

DRAM

1M X 16

Ad0-11

1of4096Decode

Ad3-7

1of32

Decode

As0-2

1of8

Decode

As0-2

1of8Decode

8X16Block

8X16Block

Upper Byte

Lower Byte

DRAM RowDecoder

16bits

As0-2

1of8Decode

Lower Byte

RB2

Lower Byte

RB1

RB1

RB2

Upper Byte

Lower Byte

WB1

DQ8-15

DQ0-7

DQ8-15

DQ0-7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V16169DRT-7 | 16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DRT-8 | 22182053 |

| M5M4V16G50DFP-10 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| M5M4V16G50DFP-12 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

| M5M4V16G50DFP-8 | 16M (2-BANK x 262144-WORD x 32-BIT) Synchronous Graphics RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V16169DRT-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DRT-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

| M5M4V16169DTP-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:16MCDRAM:16M(1M-WORD BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。