- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180233 > M58WR064HU70ZB6U 4M X 16 FLASH 1.8V PROM, 70 ns, PBGA44 PDF資料下載

參數(shù)資料

| 型號(hào): | M58WR064HU70ZB6U |

| 元件分類: | PROM |

| 英文描述: | 4M X 16 FLASH 1.8V PROM, 70 ns, PBGA44 |

| 封裝: | 7.70 X 9 MM, 0.50 MM PITCH, ROHS COMPLIANT, VFBGA-44 |

| 文件頁(yè)數(shù): | 116/117頁(yè) |

| 文件大?。?/td> | 2300K |

| 代理商: | M58WR064HU70ZB6U |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)當(dāng)前第116頁(yè)第117頁(yè)

Common Flash Interface

M58WR064HU M58WR064HL

98/117

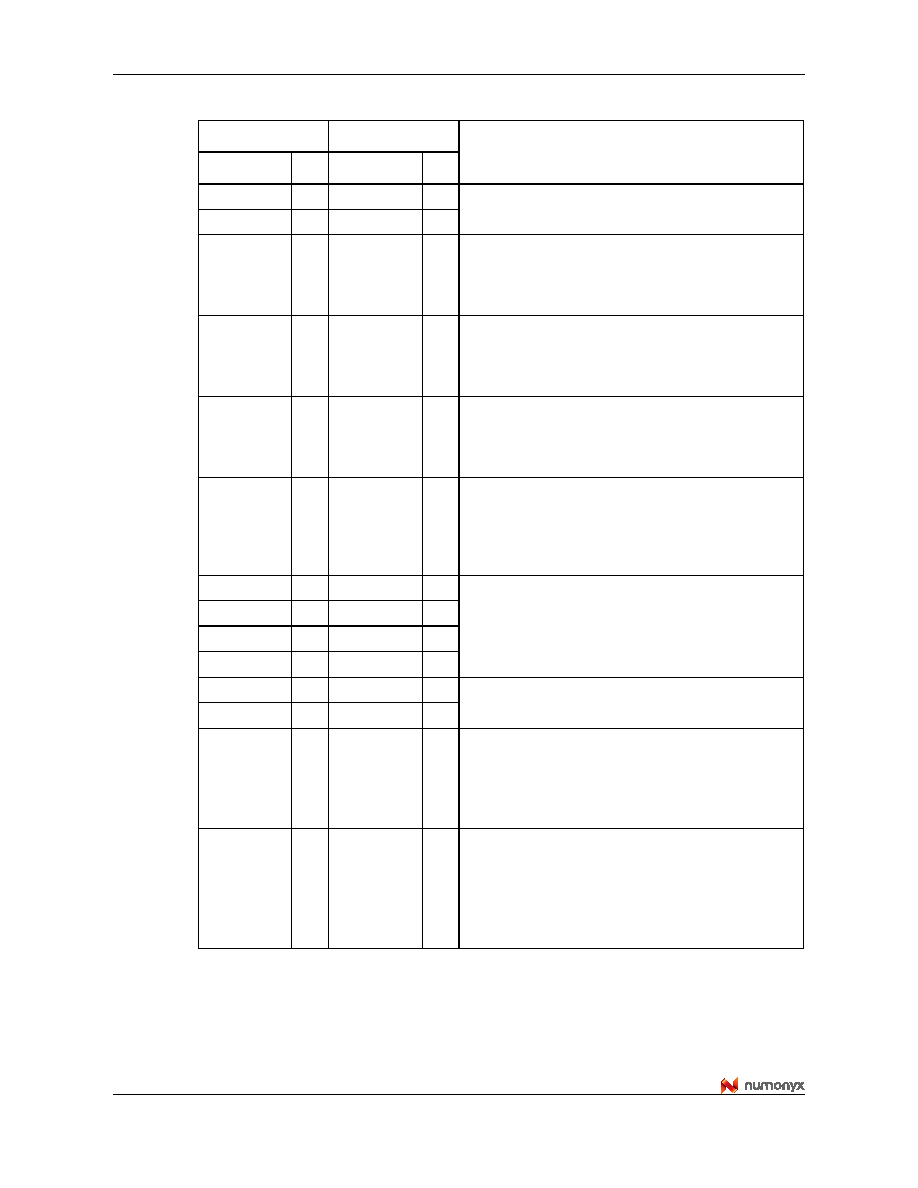

Table 42.

Bank and erase block region 2 information(1)

M58WR064HU

M58WR064HL

Description

Offset

Data

Offset

Data

(P+28)h = 61h 01h (P+30)h = 69h 0Fh

Number of identical banks within Bank Region 2

(P+29)h = 62h 00h (P+31)h = 6Ah 00h

(P+2A)h = 63h 11h (P+32)h = 6Bh 11h

Number of program or erase operations allowed in Bank

Region 2:

Bits 0-3: Number of simultaneous program operations

Bits 4-7: Number of simultaneous erase operations

(P+2B)h = 64h 00h (P+33)h = 6Ch 00h

Number of program or erase operations allowed in other

banks while a bank in this region is programming

Bits 0-3: Number of simultaneous program operations

Bits 4-7: Number of simultaneous erase operations

(P+2C)h = 65h 00h (P+34)h = 6Dh 00h

Number of program or erase operations allowed in other

banks while a bank in this region is erasing

Bits 0-3: Number of simultaneous program operations

Bits 4-7: Number of simultaneous erase operations

(P+2D)h = 66h 02h (P+35)h = 6Eh 01h

Types of erase block regions in Bank Region 2

n = number of erase block regions with contiguous same-

size erase blocks.

Symmetrically blocked banks have one blocking

region.(2)

(P+2E)h = 67h 06h (P+36)h = 6Fh 07h

Bank Region 2 Erase Block Type 1 Information

Bits 0-15: n+1 = number of identical-sized erase blocks

Bits 16-31: n×256 = number of bytes in erase block

region

(P+2F)h = 68h 00h (P+37)h = 70h 00h

(P+30)h = 69h 00h (P+38)h = 71h 00h

(P+31)h = 6Ah 01h (P+39)h = 72h 01h

(P+32)h = 6Bh 64h (P+3A)h = 73h 64h Bank Region 2 (Erase Block Type 1)

Minimum block erase cycles × 1000

(P+33)h = 6Ch 00h (P+3B)h = 74h 00h

(P+34)h = 6Dh 01h (P+3C)h = 75h 01h

Bank Region 2 (Erase Block Type 1): BIts per cell,

internal ECC

Bits 0-3: bits per cell in erase region

Bit 4: reserved for “internal ECC used”

BIts 5-7: reserved

(P+35)h = 6Eh 03h (P+3D)h = 76h 03h

Bank Region 2 (Erase Block Type 1): Page mode and

synchronous mode capabilities (defined in Table 39)

Bit 0: Page-mode reads permitted

Bit 1: Synchronous reads permitted

Bit 2: Synchronous writes permitted

Bits 3-7: reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M59DR032F100N1T | 2M X 16 FLASH 1.8V PROM, 100 ns, PDSO48 |

| M5F7924 | 24 V FIXED NEGATIVE REGULATOR, PSFM3 |

| M5F7920 | 20 V FIXED NEGATIVE REGULATOR, PSFM3 |

| M5F7918 | 18 V FIXED NEGATIVE REGULATOR, PSFM3 |

| M5F7915 | 15 V FIXED NEGATIVE REGULATOR, PSFM3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M58WR064KB70ZB6E | 制造商:Micron Technology Inc 功能描述:WIRELESS FLASH VFBGA 7.7X9.0X1.0 56 8X7 0.75 - Trays 制造商:Micron Technology Inc 功能描述:IC FLASH 64MBIT 70NS 56VFBGA |

| M58WR064KB70ZB6F | 制造商:Micron Technology Inc 功能描述:FLASH 28F640W18TD 60 VF-PBGA56 SB48 EX - Tape and Reel |

| M58WR064KB70ZB6F TR | 制造商:Micron Technology Inc 功能描述:IC FLASH 64MBIT 70NS 56VFBGA |

| M58WR064KB7AZB6E | 制造商:Micron Technology Inc 功能描述:WIRELESS - Trays 制造商:Micron Technology Inc 功能描述:IC FLASH 64MBIT 70NS 56VFBGA |

| M58WR064KB7AZB6F | 制造商:Micron Technology Inc 功能描述:WIRELESS - Tape and Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。