- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383300 > M470L6423CK0 (SAMSUNG SEMICONDUCTOR CO. LTD.) 512MB DDR SDRAM MODULE (64Mx64 based on DDP 64Mx 8 DDR SDRAM) 200pin SODIMM 64bit Non-ECC/Parity PDF資料下載

參數(shù)資料

| 型號(hào): | M470L6423CK0 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512MB DDR SDRAM MODULE (64Mx64 based on DDP 64Mx 8 DDR SDRAM) 200pin SODIMM 64bit Non-ECC/Parity |

| 中文描述: | 512MB的DDR SDRAM內(nèi)存模組(64Mx64基于鉑64Mx 8 DDR內(nèi)存)200pin的SODIMM 64 Non-ECC/Parity |

| 文件頁數(shù): | 7/14頁 |

| 文件大小: | 121K |

| 代理商: | M470L6423CK0 |

200pin DDR SDRAM SODIMM

M470L6423CK0

Rev. 0.0 Aug. 2001

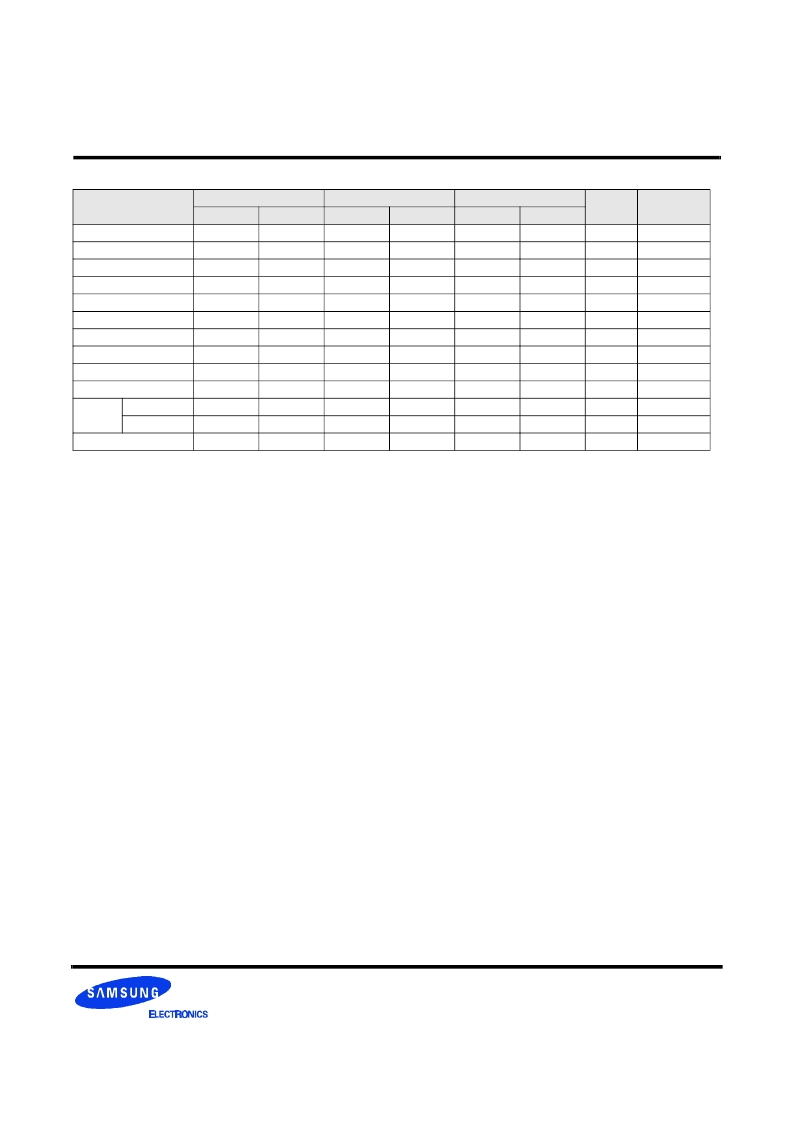

DDR SDRAM module I

DD

spec table

* Module

I

DD

was calculated on the basis of component

I

DD

and can be differently measured according to DQ loading cap.

Symbol

A2(DDR266@CL=2)

typical

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

B0(DDR266@CL=2.5)

typical

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

A0(DDR200@CL=2)

typical

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

T.B.D

Unit

Notes

worst

896

1216

48

432

T.B.D

280

616

1640

1520

1536

48

T.B.D

2760

worst

896

1216

48

432

T.B.D

280

616

1640

1520

1536

48

T.B.D

2760

worst

824

1144

48

368

T.B.D

264

544

1440

1320

1384

48

T.B.D

2280

IDD0

IDD1

IDD2P

IDD2F

IDD2Q

IDD3P

IDD3N

IDD4R

IDD4W

IDD5

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

IDD6

Normal

Low power

IDD7A

Optional

< Detailed test conditions for DDR SDRAM IDD1 & IDD7A >

IDD1 : Operating current: One bank operation

1. Typical Case : Vdd = 2.5V, T=25’C

2. Worst Case : Vdd = 2.7V, T= 10’C

3. Only one bank is accessed with tRC(min), Burst Mode, Address and Control inputs on NOP edge are changing once

per clock cycle. lout = 0mA

4. Timing patterns

- DDR200(100Mhz, CL=2) : tCK = 10ns, CL2, BL=4, tRCD = 2*tCK, tRAS = 5*tCK

Read : A0 N R0 N N P0 N A0 N - repeat the same timing with random address changing

*50% of data changing at every burst

- DDR266B(133Mhz, CL=2.5) : tCK = 7.5ns, CL=2.5, BL=4, tRCD = 3*tCK, tRC = 9*tCK, tRAS = 5*tCK

Read : A0 N N R0 N P0 N N N A0 N - repeat the same timing with random address changing

*50% of data changing at every burst

- DDR266A (133Mhz, CL=2) : tCK = 7.5ns, CL=2, BL=4, tRCD = 3*tCK, tRC = 9*tCK, tRAS = 5*tCK

Read : A0 N N R0 N P0 N N N A0 N - repeat the same timing with random address changing

*50% of data changing at every burst

Legend : A=Activate, R=Read, W=Write, P=Precharge, N=NOP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M470L6423EN | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-A2 | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-B0 | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CB3 | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CLB3 | 512MB Unbuffered SODIMM(based on sTSOP) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M470L6423EN | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-A2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-B0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CLB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。