- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370954 > M3851 (Mitsubishi Electric Corporation) Single Chip 8 Bits Microcomputer(8位單片機(jī)) PDF資料下載

參數(shù)資料

| 型號(hào): | M3851 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | Single Chip 8 Bits Microcomputer(8位單片機(jī)) |

| 中文描述: | 單芯片8位單片機(jī)(8位單片機(jī)) |

| 文件頁(yè)數(shù): | 20/61頁(yè) |

| 文件大小: | 904K |

| 代理商: | M3851 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

20

3851 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

Function

In conformity with Philips I

2

C-BUS

standard:

10-bit addressing format

7-bit addressing format

High-speed clock mode

Standard clock mode

In conformity with Philips I

2

C-BUS

standard:

Master transmission

Master reception

Slave transmission

Slave reception

16.1 kHz to 400 kHz (at

φ

= 4 MHz)

Table 4 Multi-master I

2

C-BUS interface functions

Item

Format

Communication mode

System clock

φ

= f(X

IN

)/2 (high-speed mode)

φ

= f(X

IN

)/8 (middle-speed mode)

MULTI-MASTER I

2

C-BUS INTERFACE

The multi-master I

2

C-BUS interface is a serial communications cir-

cuit, conforming to the Philips I

2

C-BUS data transfer format. This

interface, offering both arbitration lost detection and a synchro-

nous functions, is useful for the multi-master serial

communications.

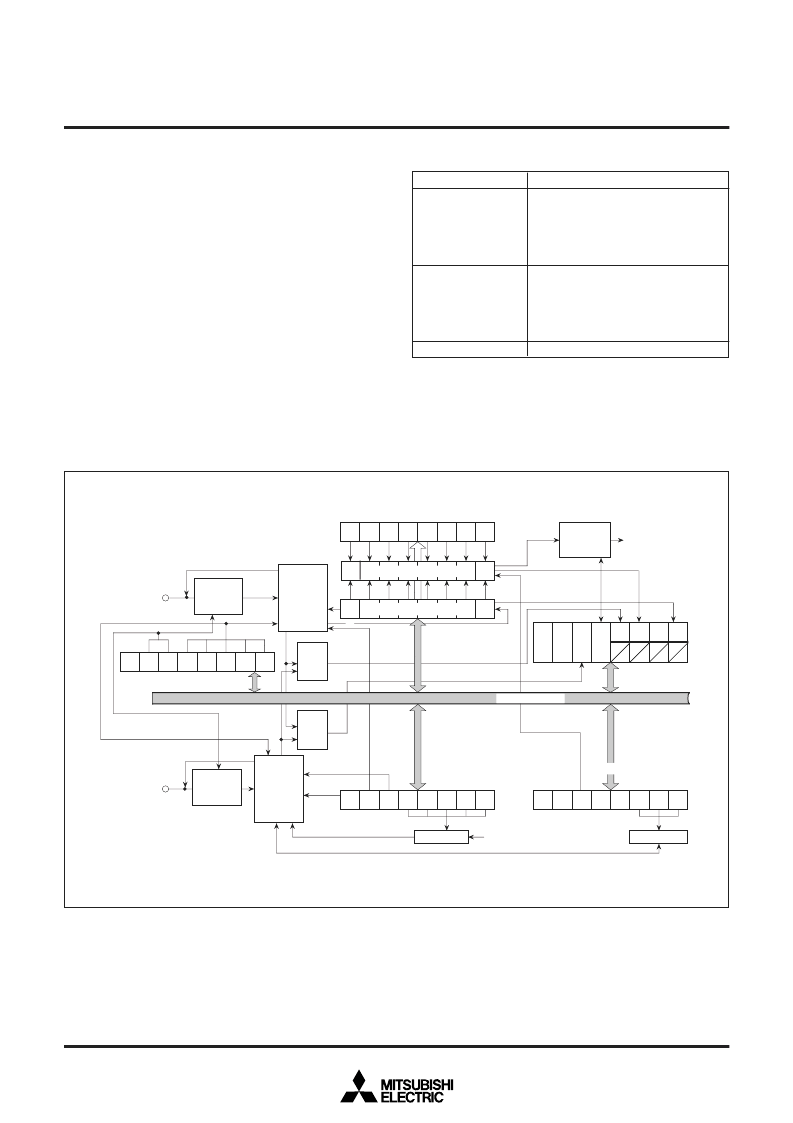

Figure 19 shows a block diagram of the multi-master I

2

C-BUS in-

terface and Table 4 lists the multi-master I

2

C-BUS interface

functions.

This multi-master I

2

C-BUS interface consists of the I

2

C address

register, the I

2

C data shift register, the I

2

C clock control register,

the I

2

C control register, the I

2

C status register, the I

2

C start/stop

condition control register and other control circuits.

When using the multi-master I

2

C-BUS interface, set 1 MHz or

more to

φ

.

Note:

Mitsubishi Electric Corporation assumes no responsibility for in-

fringement of any third-party’s rights or originating in the use of the

connection control function between the I

2

C-BUS interface and the

ports SCL

1

, SCL

2

, SDA

1

and SDA

2

with the bit 6 of I

2

C control regis-

ter (002E

16

).

Fig. 19 Block diagram of multi-master I

2

C-BUS interface

8

: Purchase of MITSUBISHI ELECTRIC CORPORATIONS I

2

C components conveys a license under the Philips I

2

C Patent Rights to use these components

an I

2

C system, provided that the system conforms to the I

2

C Standard Specification as defined by Philips.

SCL clock frequency

I

2

C address register

b7

b0

SAD6 SAD5 SAD4 SAD3 SAD2 SAD1 SAD0

RBW

Noise

elimination

circuit

Address comparator

b7

I

2

C data shift register

b0

Data

control

circuit

System clock (

φ

)

Interrupt

generating

circuit

Interrupt request signal

(IICIRQ)

b7

MST TRX BB

PIN

A

L

AAS AD0 LRB

b0

S1

b7

b0

TISS

10BIT

SAD

ALS

BC2

BC1 BC0

S1D

Bit counter

BB

circuit

Clock

control

circuit

Noise

elimination

circuit

b7

b0

ACK

ACK

BIT

FAST

MODE

CCR4 CCR3 CCR2 CCR1 CCR0

Internal data bus

Clock division

S

0

S0D

AL

circuit

ES0

SIS

I

2

C start/stop condition

control register

SIP

SSC4 SSC3 SSC2 SSC1 SSC0

I

2

S2

I

2

C status register

S2D

CLK

STP

I

2

C clock control register

S1D I C control register

Serial data

(S

DA

)

Serial

clock

(S

CL

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38512M4 | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M388504E6SP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M388504E6SS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M3850 | Single Chip 8 Bits Microcomputer(8位單片機(jī)) |

| M388504E6FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3851 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 7COND 14AWG BLK 1000' |

| M3851 BK002 | 制造商:Alpha Wire Company 功能描述:CBL 7COND 14AWG BLK 500' |

| M3851 BK005 | 制造商:Alpha Wire Company 功能描述:CBL 7COND 14AWG BLK 100' |

| M38510/00102BCB | 制造商:n/a 功能描述:38510/00102 S6I6B 制造商: 功能描述: 制造商:undefined 功能描述: |

| M38510/00103BCA | 制造商:QP Semiconductor 功能描述:NAND GATE, TRIPLE 3-INPUT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。