- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45042 > M38073E4-XXXFP 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | M38073E4-XXXFP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 0.80 MM PITCH, PLASTIC, QFP-80 |

| 文件頁數(shù): | 63/75頁 |

| 文件大?。?/td> | 1279K |

| 代理商: | M38073E4-XXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁當(dāng)前第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁

65

3807 Group

MITSUBISHI MICROCOMPUTERS

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

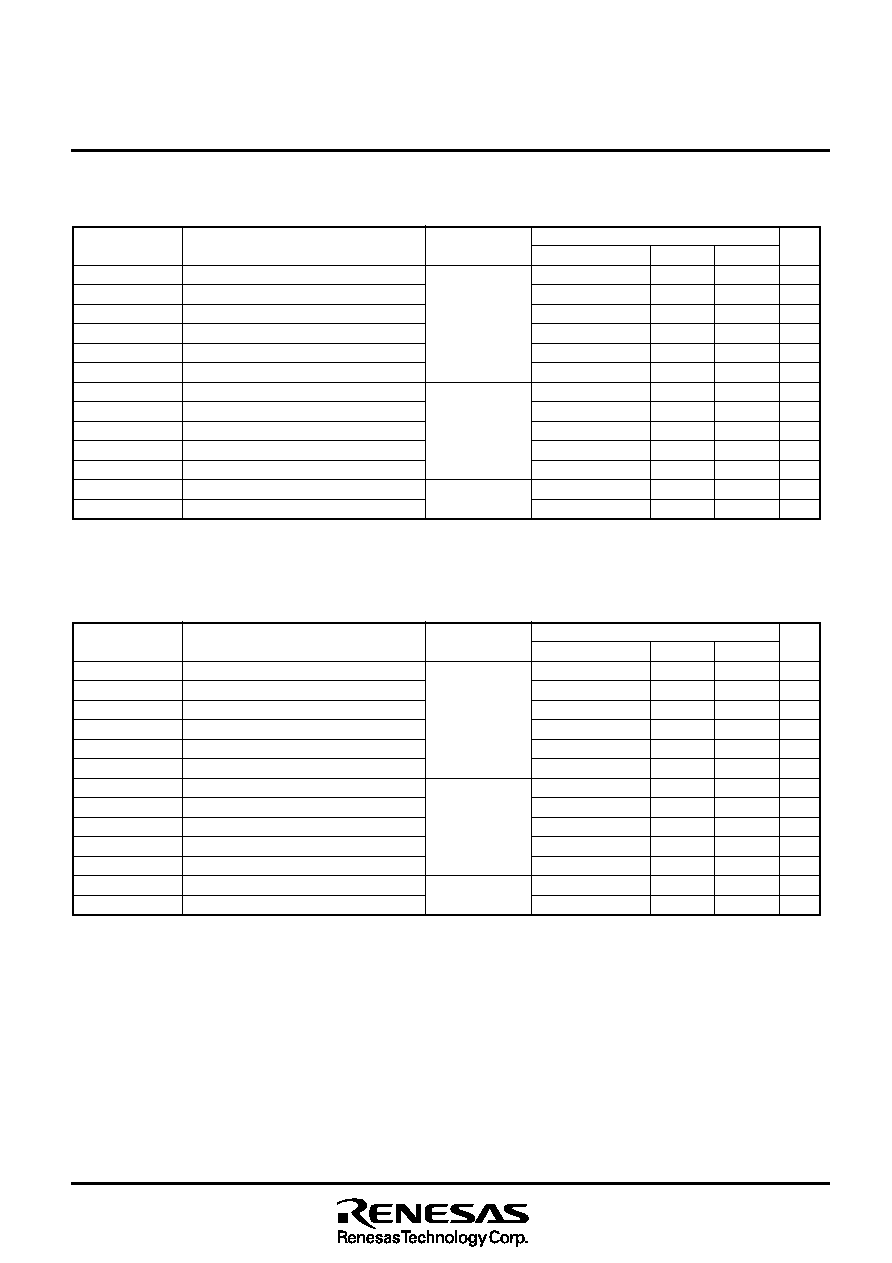

SWITCHING CHARACTERISTICS

Min.

Typ.

Max.

Symbol

Parameter

Limits

Unit

ns

tWH(SCLK1)

tWL(SCLK1)

td(SCLK1–TXD)

tv(SCLK1–TXD)

tr(SCLK1)

tf(SCLK1)

tWH(SCLK2)

tWL(SCLK2)

td(SCLK2–SOUT2)

tv(SCLK2–SOUT2)

tf(SCLK2)

tr(CMOS)

tf(CMOS)

Serial I/O1 clock output “H” pulse width

Serial I/O1 clock output “L” pulse width

Serial I/O1 output delay time (Note 1)

Serial I/O1 output valid time (Note 1)

Serial I/O1 clock output rising time

Serial I/O1 clock output falling time

Serial I/O2 clock output “H” pulse width

Serial I/O2 clock output “L” pulse width

Serial I/O2 output delay time (Note 2)

Serial I/O2 output valid time (Note 2)

Serial I/O2 clock output falling time

CMOS output rising time (Note 3)

CMOS output falling time (Note 3)

140

30

200

30

10

tC(SCLK1)/2–30

–30

tC(SCLK2)/2–160

0

Test conditions

Fig. 3.1.1

Note 1: When the P45/TD P-channel output disable bit of the UART control register (bit 4 of address 001B16) is “0”.

2: When the P71/SOUT2, P72/SCLK2 P-channel output disable bit of the serial I/O2 control register1 (bit 7 of address 001D16) is “0”.

3: XOUT pin is excluded.

Table 20 Switching characteristics (1) (Vcc = 4.0 to 5.5 V, Vss = 0 V, Ta = – 20 to 85

°C, unless otherwise noted)

Serial I/O1 clock output “H” pulse width

Serial I/O1 clock output “L” pulse width

Serial I/O1 output delay time (Note 1)

Serial I/O1 output valid time (Note 1)

Serial I/O1 clock output rising time

Serial I/O1 clock output falling time

Serial I/O2 clock output “H” pulse width

Serial I/O2 clock output “L” pulse width

Serial I/O2 output delay time (Note 2)

Serial I/O2 output valid time (Note 2)

Serial I/O2 clock output falling time

CMOS output rising time (Note 3)

CMOS output falling time (Note 3)

Min.

Typ.

Max.

Symbol

Parameter

Limits

Unit

Test conditions

tWH(SCLK1)

tWL(SCLK1)

td(SCLK1–TXD)

tv(SCLK1–TXD)

tr(SCLK1)

tf(SCLK1)

tWH(SCLK2)

tWL(SCLK2)

td(SCLK2–SOUT2)

tv(SCLK2–SOUT2)

tf(SCLK2)

tr(CMOS)

tf(CMOS)

Fig. 3.1.1

tC(SCLK1)/2–50

–30

tC(SCLK2)/2–240

0

20

350

50

400

50

ns

Note 1: When the P45/TXD P-channel output disable bit of the UART control register (bit 4 of address 001B16) is “0”.

2: When the P71/SOUT2, P72/SCLK2 P-channel output disable bit of the serial I/O2 control register1 (bit 7 of address 001D16) is “0”.

3: XOUT pin is excluded.

Table 21 Switching characteristics (2) (Vcc = 2.7 to 5.5 V, Vss = 0 V, Ta = – 20 to 85

°C, unless otherwise noted)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38073E4-XXXFP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M38073E4FP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M38073M4-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| M38073E4-XXXFP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP80 |

| M38102E5SP | 8-BIT, OTPROM, 4.19 MHz, MICROCONTROLLER, PDIP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M38078RFS | 制造商:Renesas Electronics Corporation 功能描述:EMULATION MCU/8BIT CMOS EMULATION CHIP - Bulk |

| M3808 | 功能描述:電纜固定件和配件 LTRSCG 625 BLACK RoHS:否 制造商:Heyco 類型:Cable Grips, Liquid Tight 材料:Nylon 顏色:Black 安裝方法:Cable 最大光束直徑:11.4 mm 抗拉強(qiáng)度: |

| M3808 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 10COND 18AWG BLK 1000' |

| M3808 BK002 | 制造商:Alpha Wire Company 功能描述:CBL 10COND 18AWG BLK 500' |

| M3808 BK005 | 制造商:Alpha Wire Company 功能描述:CBL 10COND 18AWG BLK 100' |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。