- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370847 > M37702S1BFP (Mitsubishi Electric Corporation) Single Chip 16 Bits CMOS Microcomputer(16位單片機(jī)) PDF資料下載

參數(shù)資料

| 型號(hào): | M37702S1BFP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | Single Chip 16 Bits CMOS Microcomputer(16位單片機(jī)) |

| 中文描述: | 單片微機(jī)16位的CMOS(16位單片機(jī)) |

| 文件頁數(shù): | 31/59頁 |

| 文件大?。?/td> | 811K |

| 代理商: | M37702S1BFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

31

MITSUBISHI MICROCOMPUTERS

M37702M2AXXXFP, M37702M2BXXXFP

M37702S1AFP, M37702S1BFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

ASYNCHRONOUS SERIAL

COMMUNICATION

Asynchronous serial communication can be performed using 7-,

8-, or 9-bit length data. The operation is the same for all data

lengths. The following is the description for 8-bit asynchronous

communication.

With 8-bit asynchronous communication, the bit 0 of UARTi trans-

mit/receive mode register is “1“, the bit 1 is “0”, and the bit 2 is “1”.

Bit 3 is used to select an internal clock or an external clock. If bit 3

is “0”, an internal clock is selected and if bit 3 is “1”, then external

clock is selected. If an internal clock is selected, the bit 0 (CS

0

)

and bit 1 (CS

1

) of UARTi transmit/receive control register 0 are

used to select the clock source. When an internal clock is selected

for asynchronous serial communication, the CLKi pin can be used

as a normal I/O pin.

The selected internal or external clock is divided by (n +1), then by

16, and passed through a control circuit to create the UART trans-

mission clock or UART receive clock.

Therefore, the transmission speed can be changed by changing

the contents n of the bit rate generator. If the selected clock is an

internal clock fi or an external clock f

EXT

,

Bit Rate = (f

i

or f

EXT

) / {(n

+

1)

16}

Bit 4 is the stop bit length selection bit to select 1 stop bit or 2 stop

bits.

The bit 5 is a selection bit of odd parity or even parity.

In the odd parity mode, the parity bit is adjusted so that the sum of

the 1’s in the data and parity bit is always odd.

In the even parity mode, the parity bit is adjusted so that the sum

of the 1’s in the data and parity bit is always even.

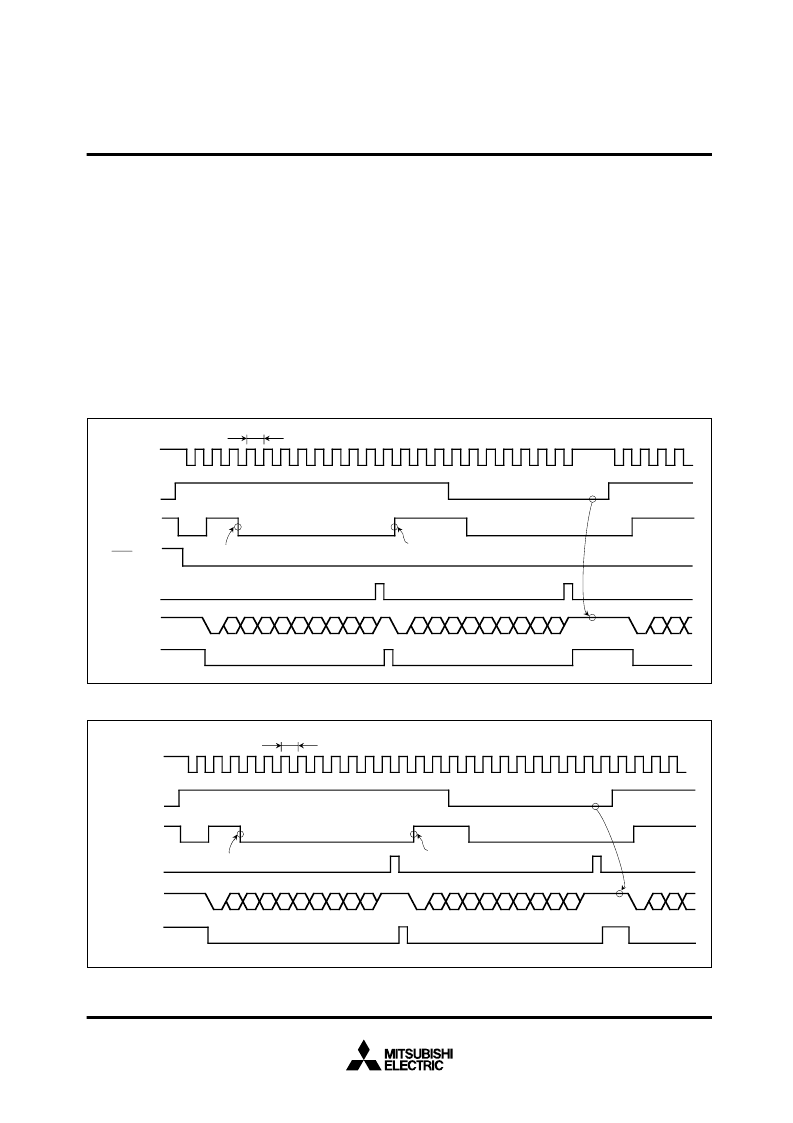

Fig. 40 Transmit timing example when 8-bit asynchronous communication with parity and 1 stop bit is selected

Fig. 41 Transmit timing example when 9-bit asynchronous communication with no parity and 2 stop bits is selected

D

6

D

7

ST

D

1

D

2

D

3

D

4

D

5

P

SP ST

STD

0

D

1

TE

i

(1 / f

1

, or 1 / f

EXT

)

(n + 1)

16

Transmission clock

CTS

i

Write in transmission buffer register

TI

i

T

ENDi

T

X

D

i

T

X

EPTY

i

Transmission register

←

Transmission

buffer register

Stopped because TEi = “0”

Start bit

Parity bit Stop bit

D

0

D

6

D

7

D

1

D

2

D

3

D

4

D

5

P

SP

D

0

TE

i

Transmission clock

TI

i

T

ENDi

T

X

D

i

T

X

EPTY

i

(1 / f

1

or 1 / f

EXT

)

(n + 1)

16

Write in transmission buffer register

Transmission register

Transmission

buffer register

Stopped because

TEi = “0”

ST D

0

D

1

Start bit

Stop Bit Stop Bit

D

6

ST

D

1

D

2

D

3

D

4

D

5

D

8

SP

D

0

D

6

D

7

D

1

D

2

D

3

D

4

D

5

SP

D

0

D

7

SP

SP

D

8

ST

D

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37702M2A | Single Chip 16 Bits CMOS Microcomputer(16位單片機(jī)) |

| M37702M2B | Single Chip 16 Bits CMOS Microcomputer(16位單片機(jī)) |

| M37702M2AXXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2A-278FP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2A-XXXFP | DIODE SCHOTTKY DUAL SERIES 50V 150mW 0.41V-vf 70mA-IFM 1mA-IF 0.1uA-IR SOT-523 3K/REEL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37702S1LGP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702S1LHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702S4AFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702S4BFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702TL-HPD | 制造商:Renesas Electronics Corporation 功能描述:DEV 7702 GROUP 25MHZ EMUL POD (LOW VOLTA - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。