- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370847 > M37702M2A-278FP (Mitsubishi Electric Corporation) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M37702M2A-278FP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單片16位CMOS微機(jī) |

| 文件頁數(shù): | 43/59頁 |

| 文件大?。?/td> | 811K |

| 代理商: | M37702M2A-278FP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

43

MITSUBISHI MICROCOMPUTERS

M37702M2AXXXFP, M37702M2BXXXFP

M37702S1AFP, M37702S1BFP

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

ALE is an address latch enable signal used to latch the address

signal from a multiplexed signal of address and data. The latch is

transparent while ALE is “H” to let the address signal pass through

_____

when the microcomputer receives HOLD input and enters into

hold state.

Ports P4

0

and P4

1

become HOLD and RDY input pin respectively

and lose their output pin function, but the input pin function re-

HOLD is a hold request signal. It is an input signal used to put the

microcomputer in hold state. HOLD input is accepted when the in-

ternal clock

φ

falls from “H” level to “L” level while the bus is not

used. Ports P0, P1, P2, P3

0

, and P3

1

are floating while the micro-

computer stays in hold state. These ports are floating after one

cycle of the internal clock

φ

later than HLDA signal changes to “L”

level. At the removing of hold state, these ports are removed from

floating state after one cycle of

φ

later than HLDA signal changes

RDY is a ready signal. If this signal goes “L”, the internal clock

φ

stops at “L”. When

φ

1

output from port P4

2

is selected by setting

bit 7 of processor mode register to “1”,

φ

1

output keeps on. RDY is

used when slow external memory is attached.

(3) Microprocessor mode [10]

Microprocessor mode is entered by connecting the CNV

SS

pin to

V

CC

and starting from reset. It can also be entered by program-

ming the processor mode bits to “10” after connecting the CNV

SS

pin to V

SS

and starting from reset. This mode is similar to memory

expansion mode except that internal ROM is disabled and an ex-

ternal memory is required, and

φ

1

from port P4

2

is always output

in spite of bit 7 of processor mode register.

(4) Evaluation chip mode [11]

Evaluation chip mode is entered by applying voltage twice the V

CC

voltage to the CNV

SS

pin. This mode is normally used for evalua-

tion tools.

The functions of ports P0 and P3 are the same as in memory ex-

pansion mode.

Port P1 functions as an address output pin while E is “H” and as

data I/O pin of odd addresses while E is “L” regardless of the

BYTE pin level. However, if an internal memory is read, external

data is ignored while E is “L”.

Port P2 function as an address output pin while E is “H” and as

data I/O pin of even addresses while E is “L” when the BYTE pin

level is “L”. However, if an internal memory is read, external data

is ignored while E is “L”.

When the BYTE pin level is “H” or 2·V

CC

, port P2 functions as an

address output pin while E is “H” and as data I/O pin of even and

odd addresses while E is “L”. However, if an internal memory is

read, external data is ignored while E is “L”.

Port P4 and its data direction register which are located at ad-

dress 0A

16

and 0C

16

are treated differently in evaluation chip

mode. When these addresses are accessed, the data bus width is

treated as 16 bits regardless of the BYTE pin level, and the ac-

cess cycle is treated as internal memory regardless of the wait bit.

When a voltage twice the V

CC

voltage is applied to the BYTE pin,

the addresses corresponding to the internal ROM area are also

treated as 16-bit data bus.

The functions of ports P4

0

and P4

1

are the same as in memory

expansion mode.

Ports P4

2

to P4

6

become

φ

1

, MX, QCL, VDA, and VPA output pins

respectively. Port P4

7

becomes the DBC input pin.

φ

1

from port P4

2

divided the clock to X

IN

pin by 2 is always output

in spite of bit 7 of processor mode register.

The MX signal normally contains the contents of flag m, but the

contents of flag x is output if the CPU is using flag x.

QCL is the queue buffer clear signal. It becomes “H” when the in-

struction queue buffer is cleared, for example, when a jump

instruction is executed.

VDA is the valid data address signal. It becomes “H” while the

CPU is reading data from data buffer or writing data to data buffer.

It also becomes “H” when the first byte of the instruction (opera-

tion code) is read from the instruction queue buffer.

VPA is the valid program address signal. It becomes “H” while the

CPU is reading an instruction code from the instruction queue

____

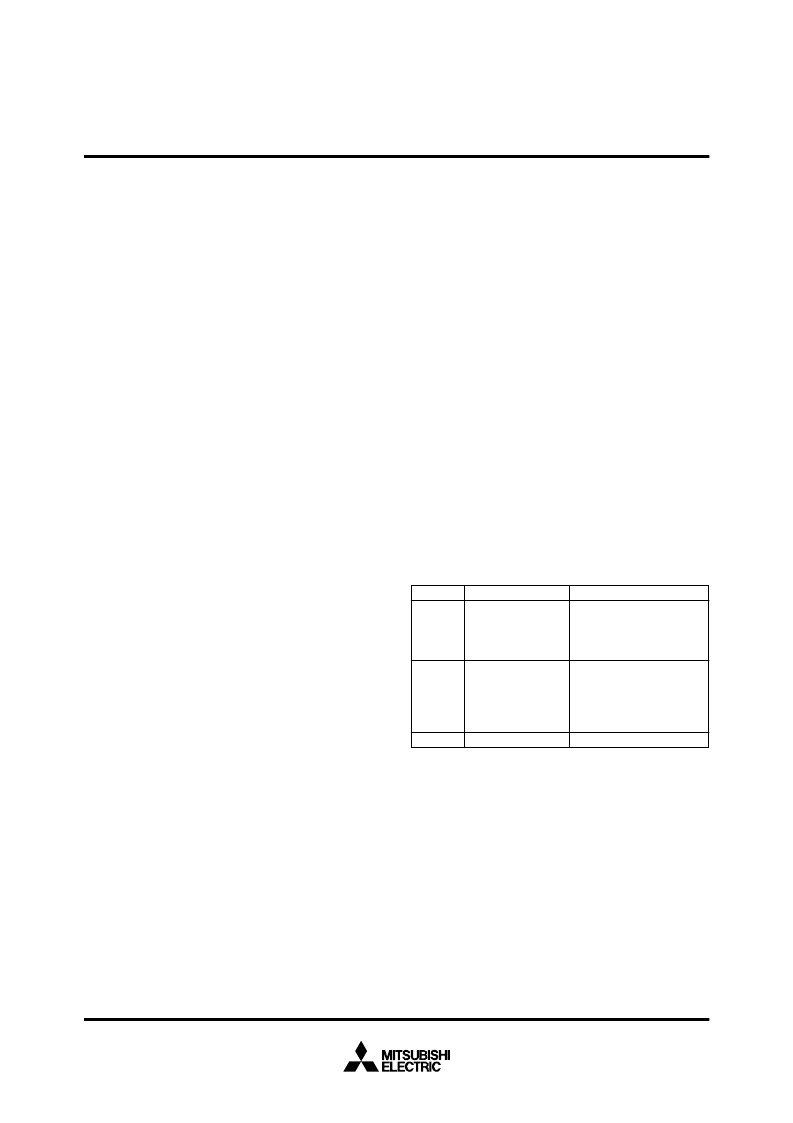

5 shows the relationship between the CNV

SS

pin input levels and

processor modes.

CNV

SS

Mode

Single-chip

Memory expansion

Microprocessor

Evaluation chip

Microprocessor

Evaluation chip

Evaluation chip

Description

Single-chip mode upon

starting after reset. Other

modes can be selected by

changing the processor

mode bit by software.

Microprocessor mode upon

starting after reset. Evalua-

tion chip mode can be

selected by changing the

processor mode bit by soft-

ware.

Evaluation chip mode only.

V

SS

V

CC

2·V

CC

Table 5. Relationship between the CNV

SS

pin input levels and

processor modes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37702M2A-XXXFP | DIODE SCHOTTKY DUAL SERIES 50V 150mW 0.41V-vf 70mA-IFM 1mA-IF 0.1uA-IR SOT-523 3K/REEL |

| M37702M2B-XXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2BXXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2L-249HP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702S1LGP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37702M2AXXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2A-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2BXXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2B-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37702M2L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。