- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370847 > M37641F8-XXXHP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M37641F8-XXXHP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁數(shù): | 10/149頁 |

| 文件大?。?/td> | 1997K |

| 代理商: | M37641F8-XXXHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁

10

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

7641 Group

PRELIMINARY

Notice: This is not a final specification.

change.

Some parametric limits are subject to

[Processor status register (PS)]

The processor status register is an 8-bit register consisting of 5 flags

which indicate the status of the processor after an arithmetic opera-

tion and 3 flags which decide MCU operation. Branch operations can

be performed by testing the Carry (C) flag , Zero (Z) flag, Overflow

(V) flag, or the Negative (N) flag. In decimal mode, the Z, V, N flags

are not valid.

Bit 0: Carry flag (C)

The C flag contains a carry or borrow generated by the arithmetic

logic unit (ALU) immediately after an arithmetic operation. It can

also be changed by a shift or rotate instruction.

Bit 1: Zero flag (Z)

The Z flag is set if the result of an immediate arithmetic operation

or a data transfer is

“

0

”

, and cleared if the result is anything other

than

“

0

”

.

Bit 2: Interrupt disable flag (I)

The I flag disables all interrupts except for the interrupt

generated by the BRK instruction.

Interrupts are disabled when the I flag is

“

1

”

.

Bit 3: Decimal mode flag (D)

The D flag determines whether additions and subtractions are

executed in binary or decimal. Binary arithmetic is executed when

this flag is

“

0

”

; decimal arithmetic is executed when it is

“

1

”

.

Decimal correction is automatic in decimal mode. Only the ADC

Bit 4: Break flag (B)

The B flag is used to indicate that the current interrupt was

generated by the BRK instruction. The BRK flag in the processor

status register is always

“

0

”

. When the BRK instruction is used to

generate an interrupt, the processor status register is pushed

onto the stack with the break flag set to

“

1

”

.

Bit 5: Index X mode flag (T)

When the T flag is

“

0

”

, arithmetic operations are performed

between accumulator and memory. When the T flag is

“

1

”

, direct

arithmetic operations and direct data transfers are enabled

between memory locations.

Bit 6: Overflow flag (V)

The V flag is used during the addition or subtraction of one byte

of signed data. It is set if the result exceeds +127 to -128. When

the BIT instruction is executed, bit 6 of the memory location

operated on by the BIT instruction is stored in the overflow flag.

Bit 7: Negative flag (N)

The N flag is set if the result of an arithmetic operation or data

transfer is negative. When the BIT instruction is executed, bit 7 of

the memory location operated on by the BIT instruction is stored

in the negative flag.

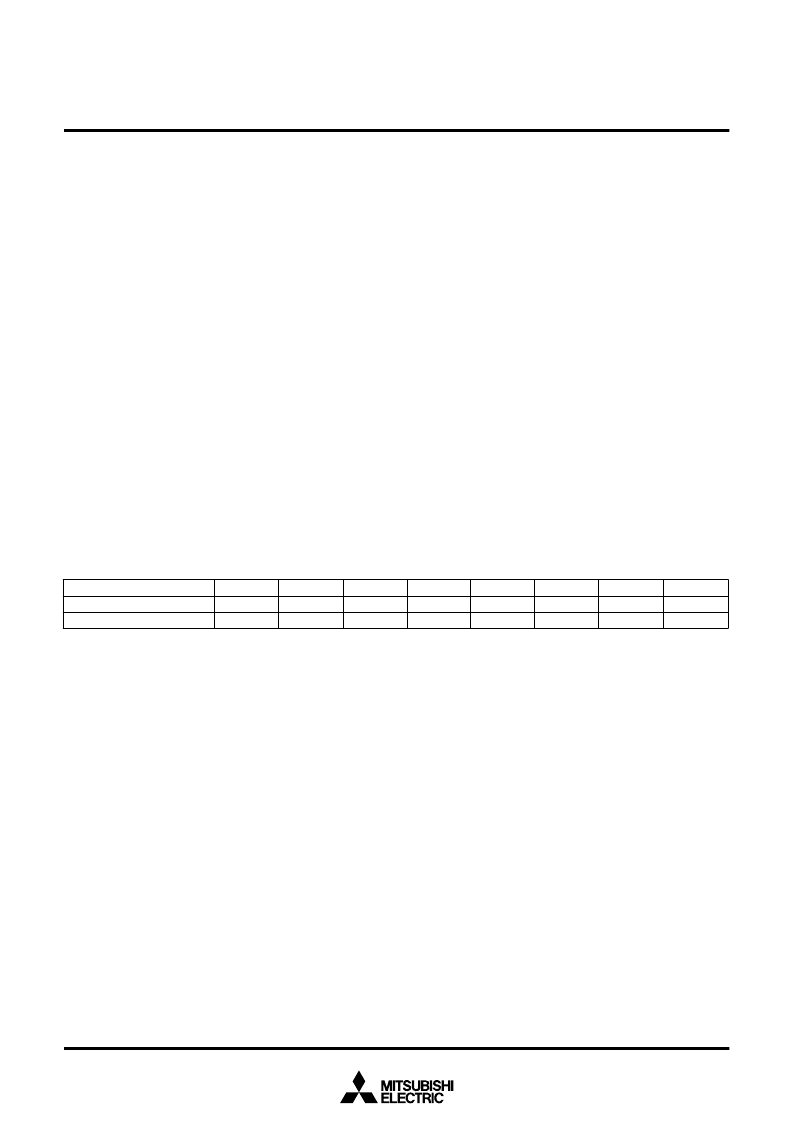

Table 5 Set and clear instructions of each bit of processor status register

C flag

SEC

CLC

Set instruction

Clear instruction

Z flag

–

–

I flag

SEI

CLI

D flag

SED

CLD

B flag

–

–

T flag

SET

CLT

V flag

–

CLV

N flag

–

–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37641M8-XXXFP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641M8 | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641F8FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641F8HP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641M8-100FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37641M8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641M8-100FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641M8E8-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641M8M8-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37641M8-XXXFP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。