- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45030 > M37225ECSP 8-BIT, OTPROM, 8.1 MHz, MICROCONTROLLER, PDIP42 PDF資料下載

參數(shù)資料

| 型號(hào): | M37225ECSP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, OTPROM, 8.1 MHz, MICROCONTROLLER, PDIP42 |

| 封裝: | 0.600 INCH, 1.78 MM PITCH, PLASTIC, SDIP-42 |

| 文件頁(yè)數(shù): | 78/128頁(yè) |

| 文件大小: | 1481K |

| 代理商: | M37225ECSP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)當(dāng)前第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)

M37225M6/M8/MA/MC-XXXSP, M37225ECSP

Rev.1.00

Nov 01, 2000

page 51 of 124

REJ03B0136-0100Z

Note: VREF indicates the reference voltage (= Vcc).

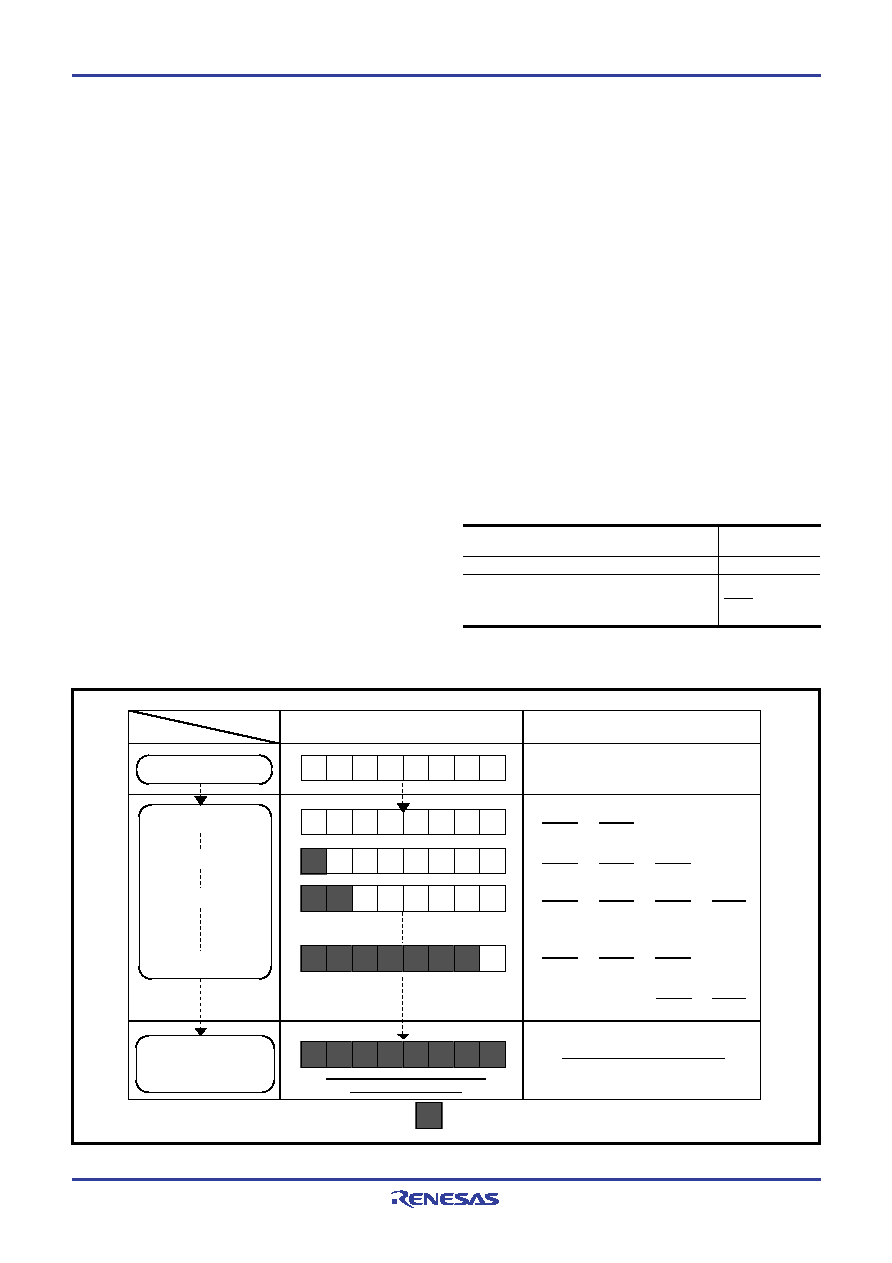

Fig. 8.8.3 Changes in A-D Conversion Register and Comparison Voltage during A-D Conversion

8.8.6 Conversion Method

Set the A-D conversion interrupt request bit to “0” (even when A-

D conversion is started, the A-D conversion interrupt reguest bit

is not set to “0” automatically).

When using A-D conversion interrupt, enable interrupts by setting

A-D conversion interrupt enable bit to “1” and setting the interrupt

disable flag to “0.”

Set the VCC connection selection bit to “1” to connect VCC to the

resistor ladder.

Select analog input pins by the analog input selection bit of the

A-D control register.

Set the A-D conversion completion bit to “0.” This write operation

starts the A-D conversion. Do not read the A-D conversion regis-

ter during the A-D conversion.

Verify the completion of the conversion by the state (“1”) of the

A-D conversion completion bit, the state (“1”) of A-D conversion

interrupt reguest bit, or the occurrence of an A-D conversion in-

terrupt.

Read the A-D conversion register to obtain the conversion re-

sults.

Note : When the ladder resistor is disconnect from VCC, set the VCC connec-

tion selection bit to “0” between steps and .

8.8.7 Internal Operation

When the A-D conversion starts, the following operations are auto-

matically performed.

The A-D conversion register is set to “0016.”

The most significant bit of the A-D conversion register becomes

“1, ” and the comparison voltage “Vref” is input to the comparator.

At this point, Vref is compared with the analog input voltage “VIN .”

Bit 7 is determined by the comparison results as follows.

When Vref < VIN : bit 7 holds “1”

When Vref > VIN : bit 7 becomes “0”

With the above operations, the analog value is converted into a digi-

tal value. The A-D conversion terminates in a maximum of 50 ma-

chine cycles (8.5

s at f(XIN) = 8 MHz) after it starts, and the conver-

sion result is stored in the A-D conversion register.

An A-D conversion interrupt request occurs at the same time as A-D

conversion completion, the A-D conversion interrupt request bit be-

comes “1.” The A-D conversion completion bit also becomes “1.”

Table 8.8.1 Expression for Vref and VREF

A-D conversion register contents “n”

(decimal notation)

0

1 to 255

Vref (V)

0

VREF

2

VREF

512

VREF

2

VREF

4

VREF

512

VREF

2

VREF

4

VREF

8

VREF

512

VREF

2

VREF

4

VREF

8

VREF

512

VREF

256

12 3 456 7 8

1 0000 0 0 0

12

100

0 0

0

1000

0 0

0

1

12 3 4 5 6

7 1

–

±

–

±±

0 000 0

0 0 0

Contents of A-D conversion register

Reference voltage (Vref)

[V]

0

A-D conversion start

1st comparison start

3rd comparison start

8th comparison start

2nd comparison start

Digital value corresponding to

analog input voltage.

A-D conversion completion

(8th comparison completion)

±±

±

–

±

.......

: Value determined by mth (m = 1 to 8) result

m

.....

VREF

256

(n – 0.5)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37250M6-XXXSP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDIP64 |

| M37260E6FP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| M37260M6-XXXFP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| M37260E6-XXXSP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP52 |

| M37270EFSP | 8-BIT, OTPROM, 8.1 MHz, MICROCONTROLLER, PDIP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37225M6 | 制造商:RENESAS 制造商全稱(chēng):Renesas Technology Corp 功能描述:SNGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER |

| M37225M8 | 制造商:RENESAS 制造商全稱(chēng):Renesas Technology Corp 功能描述:SNGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER |

| M37225MA | 制造商:RENESAS 制造商全稱(chēng):Renesas Technology Corp 功能描述:SNGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER |

| M372429100 | 制造商:ITW Switches 功能描述:IN-RUSH |

| M372429200 | 制造商:ITW Switches 功能描述:IN-RUSH |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。