- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359054 > M3488Q1 (意法半導(dǎo)體) 256 x 256 DIGITAL SWITCHING MATRIX PDF資料下載

參數(shù)資料

| 型號(hào): | M3488Q1 |

| 廠(chǎng)商: | 意法半導(dǎo)體 |

| 英文描述: | 256 x 256 DIGITAL SWITCHING MATRIX |

| 中文描述: | 256 × 256數(shù)字切換矩陣 |

| 文件頁(yè)數(shù): | 15/18頁(yè) |

| 文件大小: | 193K |

| 代理商: | M3488Q1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

Notes :

1. About mask bits Mi0 to Mi7 a logic ”0” level meansdisabling condition, a logic”1” levelmeans enabling condition.

2. A nullmask or a RESET pulse clear the mask and thedeep background mask registers and disable channel0 extraction function.

3. Readingof OR2 is optional aftermask storeor redefinition, because function is activated only by not-null mask writing.

4. Aftermask store (N2N1N0)is the sum ofactivated channels, afterDRis thesumofactive channels ;Tn= 1/0 meansactivation/sup-

pression of thefunction after store while after DR only Tn = 1 can appear to tell a not-null configuration to be extracted.

5. Readingof OR2is imperative after DR inorder to step the data transfer ; reading ofOR1is also needed toscanin descending order

the priority register. Relevant messages only are considered, thatmeans only messages with a MSD label differentfrom 0 1.

6. (P2 P1P0) is the PCM bus on which the message copied inOR1 wasfound; Fnis a continuation bittelling respectively on level 1/0

for any more/no more extraction step to be performed.

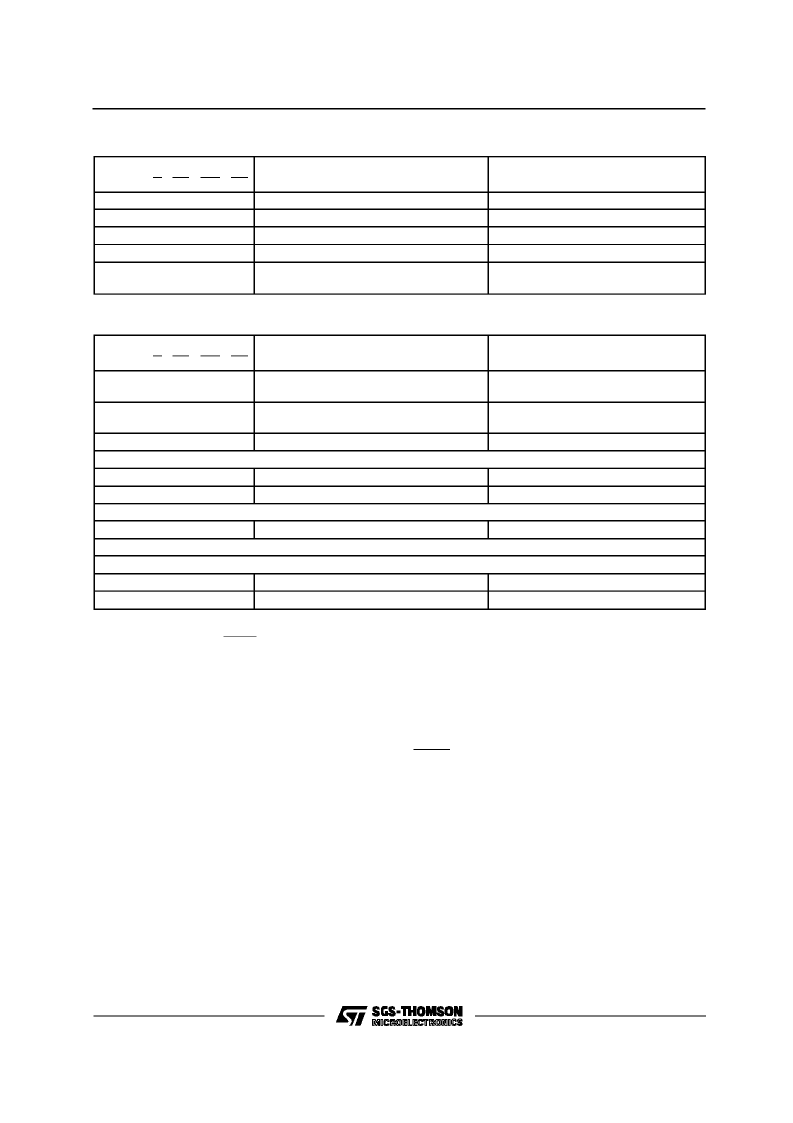

INSTRUCTION5: TRANSFER OF AN OUTPUT CHANNEL CONTROL WORD

Control Signals

Match C/D

X

0

X

0

Yes

1

Yes

0

Data Bus

D4

X

Co4 Co3 Co2 Co1 Co0 2

nd

Data Byte: selected output channel.

X

1

0

0

0

Instruction Opcode

C4

C3

C2

C1

C0

OR1: CM selected CM word copy.

C8

C8

1

0

0

0)

Notes

CS

0

0

0

0

WR

0

0

0

1

RD

1

1

1

0

D7

X

X

X

C7

A7

(Bo2

D6

X

X

X

C6

A6

Bo1

D5

X

X

X

C5

A5

Bo0

D3

X

D2

Bo2 Bo1 Bo0

D1

D0

1

st

Data Byte: selected output bus.

Yes

1

0

1

0

1

0

0

0

OR2: that is.

INSTRUCTION6: CHANNEL 0 SELECTION MASK STORE/DATA TRANSFER

Control Signals

Match C/D

Data Bus

D4

Notes

CS

WR

RD

D7

D6

D5

D3

D2

D1

D0

X

0

0

0

1

X

X

X

X

X

Mi7

Mi6

Mi5

1

st

Data Byte: most sign. digits of

selection mask.

2

nd

Data Byte: least sign. digits of

selection mask.

Instruction Opcode

X

0

0

0

1

X

X

X

Mi4

Mi3

Mi2

Mi1

Mi0

Yes

Mask store control

Yes

0

Yes

1

First Data Transfer

(after DR going low)

Yes

0

0

Yes

1

0

Repeated Data Transfer

(after first OR2 transfer)

Yes

0

0

1

Yes

1

0

1

1

0

0

1

X

X

X

X

1

1

1

0

0

0

1

1

0

0

(previous content)

N0

Tn

OR1: register is not affected.

OR2: see below.

N2

N1

1

1

1

0

1

1

0

0

(previous content)

N0

Tn

OR1: register is not affected.

OR2: see below.

N2

N1

1

1

1

0

0

0

S7

P2

S6

P1

S5

P0

S4

Fn

S3

1

S2

1

S1

1

S0

0

OR1: expected message stored in SM.

OR2: see below.

M3488WITH LESS PCM LINKS THAN 32

CHANNELS

It is also possible to use M3488 when the PCM

framesare made up of a number of channelsother

than 32.

Supposethat the PCM frames are made up of N-

Channels,which will be numberedfrom 0 to (N-1).

EachPCM framewill thusbe madeup of a number

of bits multiplied by8 ; this exactlyequalto (N

.

8).

Also,in this case,it is necessaryto respectthe tim-

ingrelationshipbetweenthedifferentsignalsshown

on thedatasheet; in particular, arelation-shipis al-

ways carefully made between the rising edge of

SYNC and the first clock (CK) bit contained in the

slottime for bit 0 of channel0.

In order to use M3488 with theseframes, it is suffi-

cient, usingthe databytessentbythemicroproces-

sor, to modify the numberingof a few channels.

In particular :

a)inallinstructionsinwhichreferenceismadetothe

input channel (N-1), the number 31 should be

substitutedfor thenumber(N-1) ;

b)inallinstructionsinwhichreferenceismadetothe

output channel 0, the number N should be sub-

stitutedfor the number0.

M3488

15/18

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M3488 | 256 x 256 DIGITAL SWITCHING MATRIX |

| M3488B1 | 256 x 256 DIGITAL SWITCHING MATRIX |

| M3493B2 | CMOS 12 X 8 CROSSPOINTWITH CONTROL MEMORY |

| M3493B1 | CMOS 12 X 8 CROSSPOINTWITH CONTROL MEMORY |

| M34A08-VDW6T | 2 Kbit Serial SMBus EEPROM for ACR Card Configuration |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3489PS-H300-B300 | 制造商:Bonitron 功能描述:REGULATOR FOR VFDS |

| M34-8L | 制造商:BOWIN 制造商全稱(chēng):BOWIN 功能描述:SINGLE OUTPUT LED FLASHER IC |

| M348X | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:UM348x Multi-Instrument Melody Generator |

| M34-92 | 制造商:GAMEWELL-FCI 制造商全稱(chēng):GAMEWELL-FCI 功能描述:Three-Fold Fire Alarm Boxes and Transmitters |

| M3493 | 制造商:Tamura Corporation of America 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。