- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358968 > M14C64 (意法半導(dǎo)體) Memory Card IC 64/32 Kbit Serial IC Bus EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | M14C64 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Memory Card IC 64/32 Kbit Serial IC Bus EEPROM |

| 中文描述: | 記憶卡IC 64/32千位串行IC總線的EEPROM |

| 文件頁(yè)數(shù): | 7/14頁(yè) |

| 文件大小: | 126K |

| 代理商: | M14C64 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

7/14

M14C64, M14C32

typical time is shorter. To make use of this, an ACK

polling sequence can be used by the master.

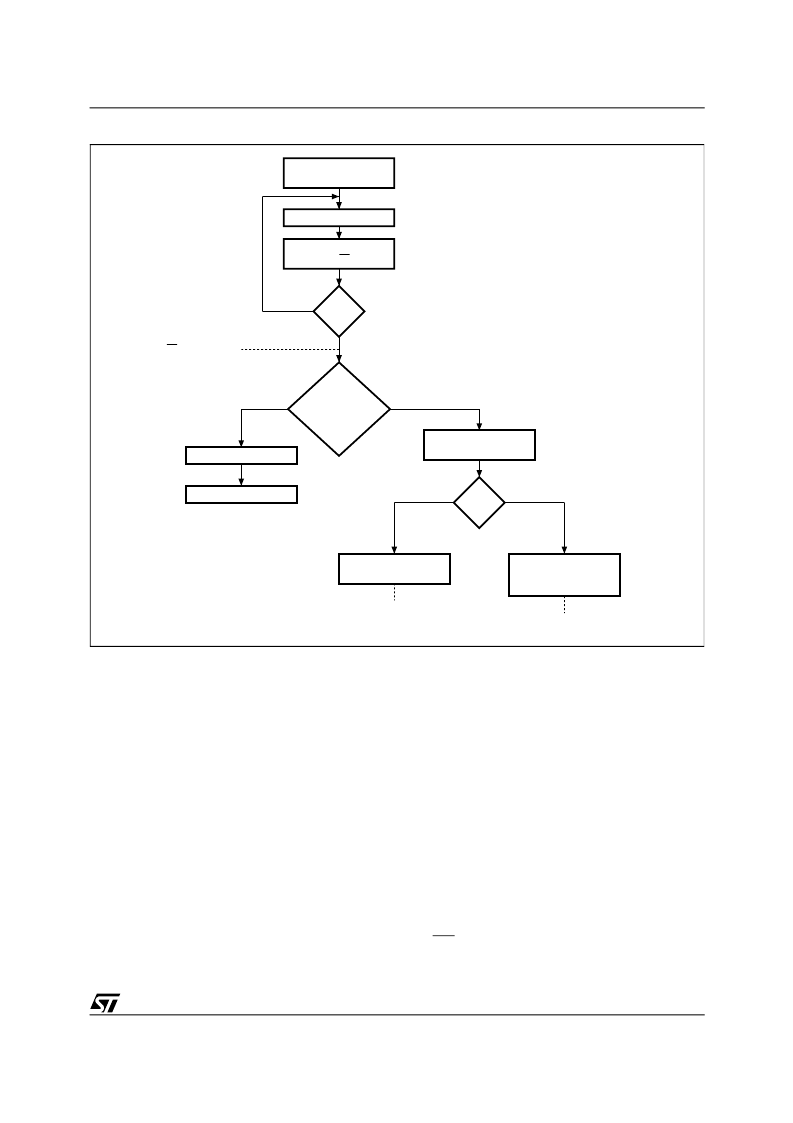

The sequence, as shown in Figure 8, is as follows:

– Initial condition: a Write is in progress.

– Step 1: the master issues a START condition

followed by a device select byte (first byte of the

new instruction).

– Step 2: if the memory is busy with the internal

write cycle, no ACK will be returned and the

master goes back to Step 1. If the memory has

terminated the internal write cycle, it responds

with an ACK, indicating that the memory is

ready to receive the second part of the next in-

struction (the first byte of this instruction having

been sent during Step 1).

Read Operations

Read operations are independent of the state of

the WC pin. On delivery, the memory content is set

at all “1’s” (FFh).

ed. The transfer is terminated by the master

generating a STOP condition. Care must be taken

to avoid address counter ’roll-over’ which could re-

sult in data being overwritten. Note that, for any

byte or page write mode, the generation by the

master of the STOP condition starts the internal

memory program cycle. This STOP condition trig-

gers an internal memory program cycle only if the

STOP condition is internally decoded immediately

after the ACK bit; any STOP condition decoded

out of this "10

th

bit" time slot will not trigger the in-

ternal programming cycle. All inputs are disabled

until the completion of this cycle and the Memory

will not respond to any request.

Minimizing System Delays by Polling On ACK

During the internal write cycle, the memory discon-

nects itself from the bus, and copies the data from

its internal latches to the memory cells. The maxi-

mum write time (t

w

) is indicated in Table 7, but the

Figure 8. Write Cycle Polling Flowchart using ACK

WRITE Cycle

in Progress

AI02165

Next

Operation is

Addressing the

Memory

START Condition

DEVICE SELECT

with RW = 0

ACK

Returned

YES

NO

YES

NO

ReSTART

STOP

Proceed

WRITE Operation

Proceed

Random Address

READ Operation

Send

Byte Address

First byte of instruction

with RW = 0 already

decoded by M14xxx

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M16C30P | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M2201 | 2-Wires 1 Kbit x8 Serial EEPROM |

| M22100 | 4 X 4 CROSSPOINT SWITCH WITH CONTROL MEMORY |

| M22102F1 | 5015 RR 4#12 SKT PLUG |

| M22102 | WITH CONTROL MEMORY 4 X 4 X 2 CROSSPOINT SWITCHES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M14D1G1664A-2.5BG2D | 制造商:ESMT 功能描述: |

| M14D2561616A | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks DDR II SDRAM |

| M14D2561616A-2.5BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks DDR II SDRAM |

| M14D2561616A-3BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:4M x 16 Bit x 4 Banks DDR II SDRAM |

| M14D5121632A | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:8M x 16 Bit x 4 Banks DDR II SDRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。