- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377801 > M12S128168A-10TG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 2M x 16 Bit x 4 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | M12S128168A-10TG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| 中文描述: | 8M X 16 SYNCHRONOUS DRAM, 7 ns, PDSO54 |

| 封裝: | 0.400 INCH, LEAD FREE, TSOP2-54 |

| 文件頁數(shù): | 24/44頁 |

| 文件大?。?/td> | 967K |

| 代理商: | M12S128168A-10TG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

ES MT

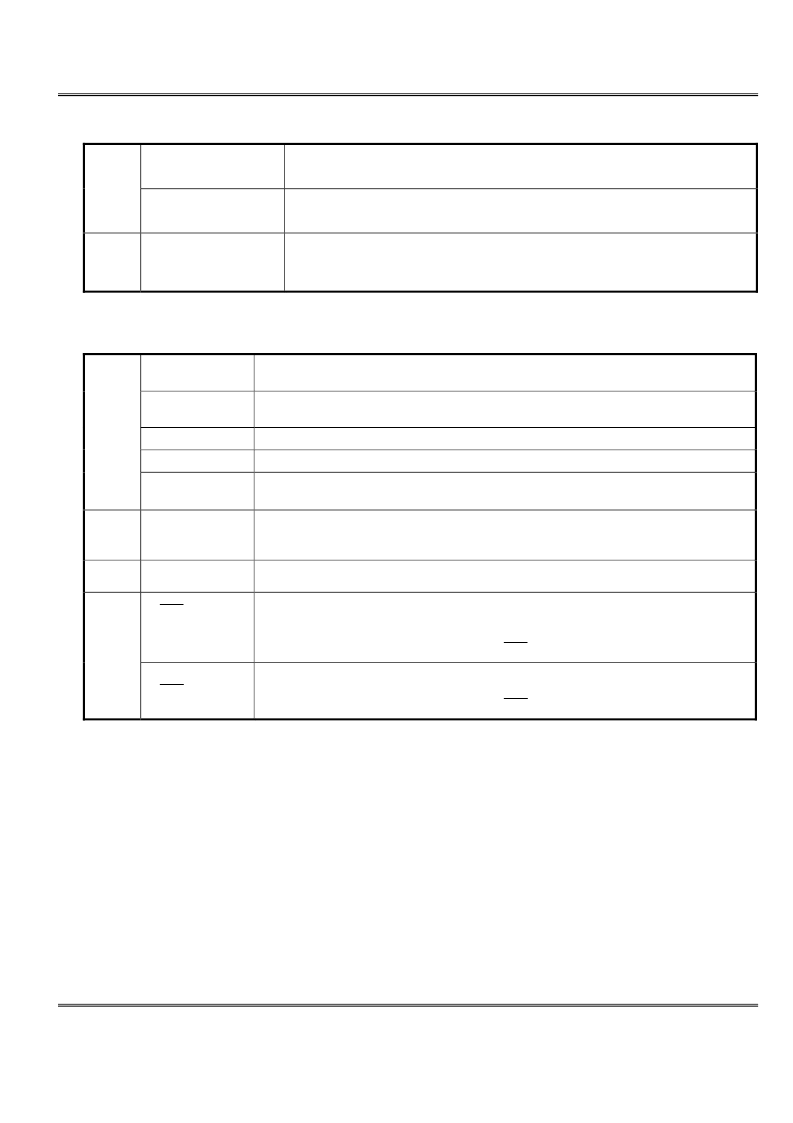

12. About Burst Type Control

M12S128168A

Elite Semiconductor Memory Technology Inc.

Revision

:

1.0

Publication Date

:

Nov. 2006

24/44

Sequential Counting

Interleave Counting

At MRS A3 = “0”. See the BURST SEQUENCE TABLE. (BL = 4,8)

BL = 1, 2, 4, 8 and full page.

Basic

MODE

At MRS A3 = “1”. See the BURST SEQUENCE TABLE. (BL = 4,8)

BL = 4, 8 At BL =1, 2 interleave Counting = Sequential Counting

Random

MODE

Random Column Access

tCCD = 1 CLK

Every cycle Read/Write Command with random column address can realize Random

Column Access.

That is similar to Extended Data Out (EDO) Operation of conventional DRAM.

13. About Burst Length Control

1

At MRS A210 = “000”

At auto precharge . t

RAS

should not be violated.

2

At MRS A210 = “001”

At auto precharge . t

RAS

should not be violated.

4

At MRS A210 = “010”

8

At MRS A210 = “011”

Basic

MODE

Full Page

At MRS A210 = “111”

At the end of the burst length , burst is warp-around.

Special

MODE

BRSW

At MRS A9 = “1”

Read burst = 1,2,4,8, full page write burst =1

At auto precharge of write, t

RAS

should not be violated.

tBDL = 1, Valid DQ after burst stop is 1, 2 for CAS latency 2, 3 respectively.

Using burst stop command, any burst length control is possible.

Random

MODE

Burst Stop

RAS Interrupt

(Interrupted by

Precharge)

Before the end of burst. Row precharge command of the same bank stops read /write burst

with auto precharge.

t

RDL

= 1 with DQM , Valid DQ after burst stop is 1, 2 for CAS latency 2, 3 respectively.

During read/write burst with auto precharge, RAS interrupt can not be issued.

Interrupt

MODE

CAS Interrupt

Before the end of burst, new read/write stops read/write burst and starts new read/write

burst.

During read/write burst with auto precharge, CAS interrupt can not be issued.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M12S16161A-7BG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M12S16161A-7TG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M12S64322A | 512K x 32 Bit x 4 Banks Synchronous DRAM |

| M12S64322A-6BG | 512K x 32 Bit x 4 Banks Synchronous DRAM |

| M12S64322A-6TG | 512K x 32 Bit x 4 Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M12S128168A-6BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S128168A-6TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S128168A-7BG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S128168A-7TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S128324A | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:1M x 32 Bit x 4 Banks Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。