- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT9863HC LAN HUB CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | LXT9863HC |

| 英文描述: | LAN HUB CONTROLLER |

| 中文描述: | 局域網(wǎng)集線器控制器 |

| 文件頁數(shù): | 12/96頁 |

| 文件大小: | 1309K |

| 代理商: | LXT9863HC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

LXT980/980A Dual-Speed, 5-Port Fast Ethernet Repeater

12

Datasheet

21

MII_TXCLK

Output

TTL

Transmit Clock.

2.5 or 25 MHz continuous output derived from the 25 MHz input clock.

20

MII_TXEN

Input

TTL

Transmit Enable.

External controllers drive this input High to indicate that data is being

transmitted on the MII_TXD<3:0> pins. Tie this input Low if it is unused.

19

18

17

16

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

Input

TTL

Transmit Data.

External controllers use these inputs to transmit data to the LXT980. The

LXT980 samples MII_TXD<3:0> on the rising edge of MII_TXCLK, when MII_TXEN is High.

14

MII_COL

Output

TTL

Collision.

The LXT980 drives this signal High to indicate that a collision has occurred.

13

MII_CRS

Output

TTL

Carrier Sense.

Active High signal indicates LXT980 is transmitting or receiving.

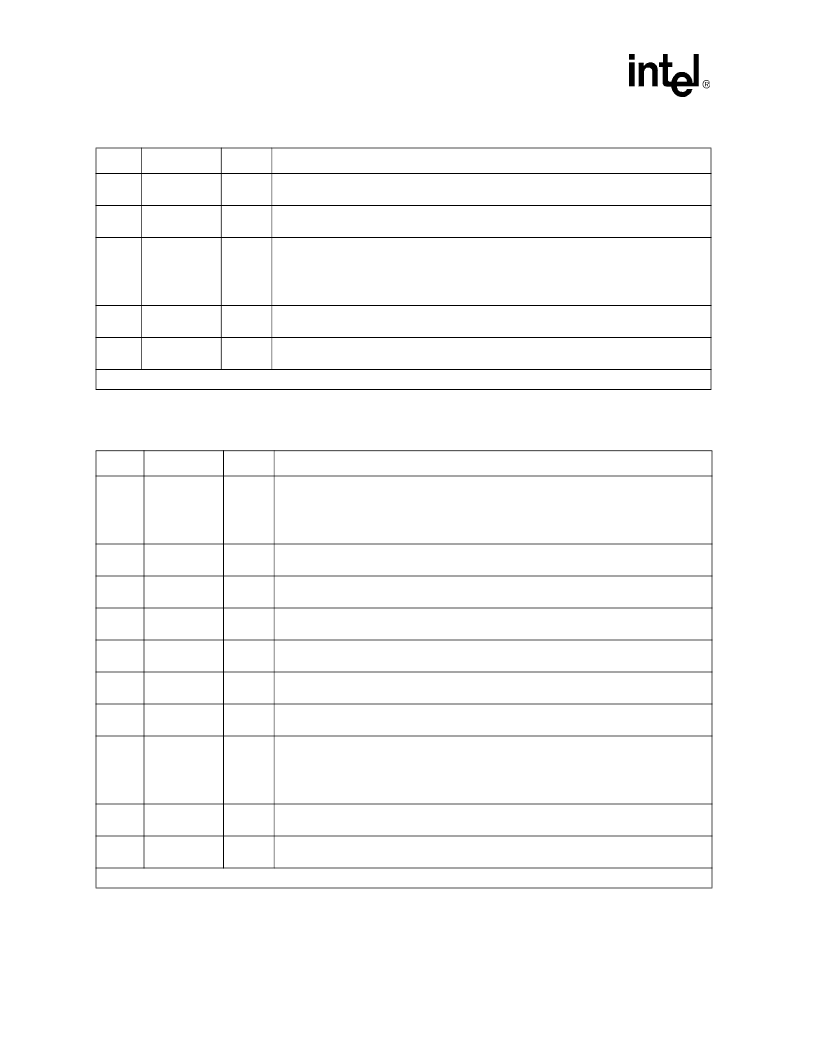

Table 3. MAC Mode MII Interface Signal Descriptions

Pin

Symbol

Type

1

Description

29

30

32

33

MII_RXD0

MII_RXD1

MII_RXD2

MII_RXD3

Input

TTL

Receive Data.

The LXT980 receives data from the PHY on these pins. Data is sampled on

the rising edge of MII_RXCLK.

26

MII_RXDV

Input

TTL

Receive Data Valid.

The PHY asserts this active High signal, synchronous to MII_RXCLK,

to indicate valid data on MII_RXD<3:0>.

25

MII_RXCLK

Input

TTL

Receive Clock.

MII receive clock for expansion port. This is a 25 MHz clock.

24

MII_RXER

Input

TTL

Receive Error.

The PHY asserts this active High signal, synchronous to MII_RXCLK, to

indicate invalid data on MII_RXD<3:0>.

22

MII_TXER

Output

TTL

Transmit Error.

The LXT980 asserts this signal when an error has occurred in the transmit

data stream.

21

MII_TXCLK

Input

TTL

Transmit Clock.

25 MHz continuous input clock. Must be supplied from same source as

CLK25 system clock.

20

MII_TXEN

Output

TTL

Transmit Enable.

The LXT980 drives this output High to indicate that data is being

transmitted on the MII_TXD<3:0> pins.

19

18

17

16

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

Output

TTL

Transmit Data.

The LXT980 drives these outputs to transmit data to the PHY. The device

drives MII_TXD<3:0> on the rising edge of MII_TXCLK, when MII_TXEN is High.

14

MII_COL

Input

TTL

Collision.

The PHY asserts this active High signal to notify the LXT980 that a collision

has occurred.

13

MII_CRS

Input

TTL

Carrier Sense.

The PHY asserts this active High signal to notify the LXT980 that the PHY

is transmitting or receiving.

1. MII interface pins reverse direction based on PHY/MAC mode. Direction listed is for MAC mode.

Table 2. PHY Mode MII Interface Signal Descriptions (Continued)

Pin

Symbol

Type

1

Description

1. MII interface pins reverse direction based on PHY/MAC mode. Direction listed is for PHY mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT9880AGE | Controller Miscellaneous - Datasheet Reference |

| LXT9880AHC | Controller Miscellaneous - Datasheet Reference |

| LXT9880HC | Controller Miscellaneous - Datasheet Reference |

| LXT9883HC | LAN HUB CONTROLLER |

| LZ1030M | Common Anode Diode Array |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT9880 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 10/100 Repeater with Intergrated Management |

| LXT9880AGE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| LXT9880AHC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| LXT9880HC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| LXT9883 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 10/100 Umnmanaged Repeater |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。