- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT9860HC Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號: | LXT9860HC |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 84/96頁 |

| 文件大小: | 1309K |

| 代理商: | LXT9860HC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁當(dāng)前第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

LXT980/980A Dual-Speed, 5-Port Fast Ethernet Repeater

84

Datasheet

5.3.2

General Port Control Registers

The General Port Control Register set is described in

Table 59

. Refer to

Table 58

for the General

Port Control Registers bit assignments.

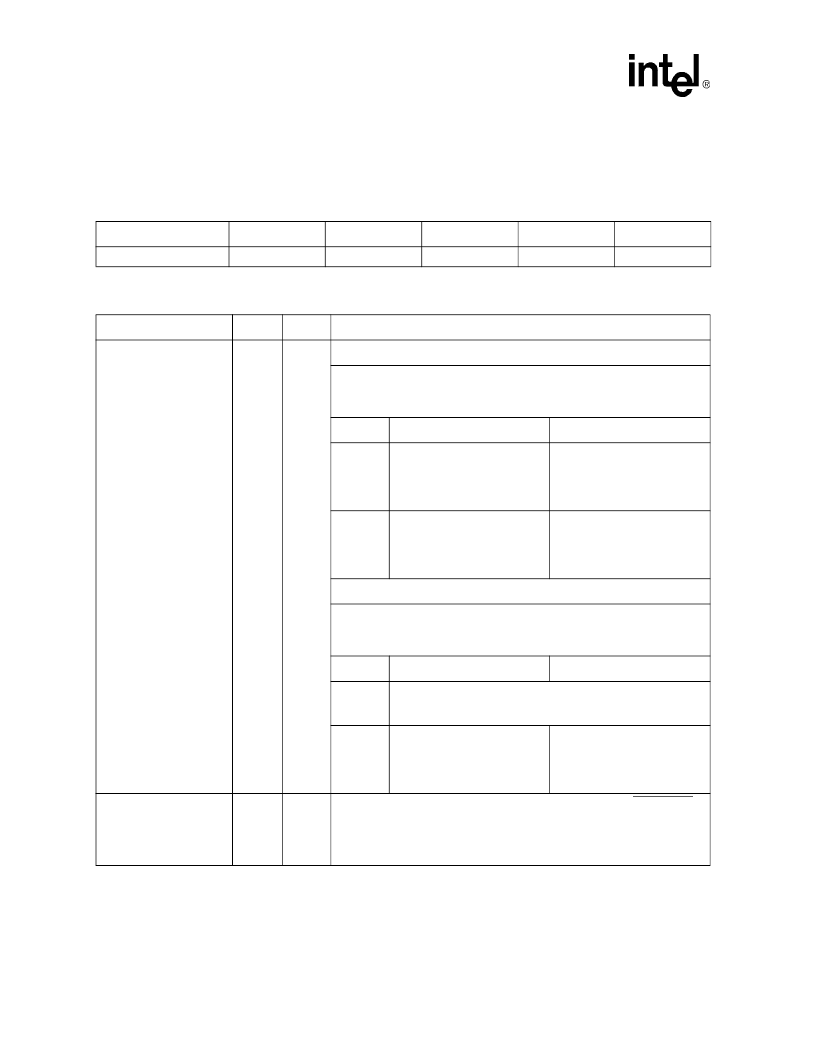

Table 58. General Port Control and Status Register Bit Assignments

31:5

4

3

2

1

0

Rsvd

Port 5 (MII)

Port 4

Port 3

Port 2

Port 1

Table 59. General Port Control Registers

Name

Type

Addr

Description

Port Alternate Partition

Algorithm Control

R/W

094

LXT980

Provides per-port selection of partition algorithms.

0 = normal (default)

1 = alternate

Speed

Normal

Alternate

10M

Un-partition a port when data

can be

either received or

transmitted

from the port for

450-560 bit times without a

collision on that port.

Un-partition a port

only when

data can be transmitted

to the

port for 450-560 bit times

without a collision on that port.

100M

Un-partition a port

only when

data can be transmitted

to the

port for 450-560 bit times

without a collision on that port.

Un-partition a port when data

can be

either received or

transmitted

from the port for

450-560 bit times without a

collision on that port.

LXT980A

Provides per-port selection of partition algorithms.

0 = normal

1 = alternate (default)

Speed

Normal

Alternate

10M

Un-partition a port when data can be

either received or

transmitted

from the port for 450-560 bit times without a collision

on that port.

100M

Un-partition a port

only when

data can be transmitted

to the

port for 450-560 bit times

without a collision on that port.

Un-partition a port when data

can be

either received or

transmitted

from the port for

450-560 bit times without a

collision on that port.

Port Enable

R/W

095

This register controls whether a port is enabled/disabled. If the MGR_PRES

signal is Low on power up, then all ports will be disabled until such time that

management software re-enables them. Otherwise the ports will power on

enabled.

0 = disable, 1 = enable (default = 1).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT9863HC | LAN HUB CONTROLLER |

| LXT9880AGE | Controller Miscellaneous - Datasheet Reference |

| LXT9880AHC | Controller Miscellaneous - Datasheet Reference |

| LXT9880HC | Controller Miscellaneous - Datasheet Reference |

| LXT9883HC | LAN HUB CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT9863 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 10/100 Umnmanaged Repeater |

| LXT9863HC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN HUB CONTROLLER |

| LXT9880 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 10/100 Repeater with Intergrated Management |

| LXT9880AGE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| LXT9880AHC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。