- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377730 > LTC1090M (Linear Technology Corporation) Single Chip 10-Bit Data Acquisition System PDF資料下載

參數(shù)資料

| 型號: | LTC1090M |

| 廠商: | Linear Technology Corporation |

| 英文描述: | Single Chip 10-Bit Data Acquisition System |

| 中文描述: | 單芯片10位數(shù)據(jù)采集系統(tǒng) |

| 文件頁數(shù): | 24/28頁 |

| 文件大小: | 344K |

| 代理商: | LTC1090M |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁

24

LTC1090

1090fc

U

TYPICAL APPLICATIO

Sneak-A-Bit Code for the LTC1090 Using the MC68HC05C4

MNEMONIC

DESCRIPTION

READ–/+: LDA

#$3F

TRANSFER Read LTC1090 routine

$60

Load MSBs from LTC1090 into ACC

$71

Store MSBs in $71

$61

Load LSBs from LTC1090 into ACC

$72

Store LSBs in $72

Return

#$7F

Load D

IN

word for LTC1090 into ACC

TRANSFER Read LTC1090 routine

$60

Load MSBs from LTC1090 into ACC

$73

Store MSBs in $73

$61

Load LSBs from LTC1090 into ACC

$74

Store LSBs in $74

Return

TRANSFER:BCLR 0, $02

CS goes low

STA

$0C

Load D

IN

into SPI. Start transfer

LOOP 1:

TST

$0B

Test status of SPlF

BPL

LOOP 1

Loop to previous instruction if not done

LDA

$0C

Load contents of SPI data reg into ACC

STA

$0C

Start next cycle

STA

$60

Store MSBs in $60

LOOP 2:

TST

$0B

Test status of SPlF

BPL

LOOP 2

Loop to previous instruction if not done

BSET 0, $02

CS goes high

LDA

$0C

Load contents of SPI data reg into ACC

STA

$61

Store LSBs in $61

RTS

Return

CHK SIGN: LDA

$73

Load MSBs of +/–read into ACC

ORA

$74

Or ACC (MSBs) with LSBs of +/–read

BEQ

MINUS

If result is 0 goto minus

CLC

Clear carry

ROR

$73

Rotate right $73 through carry

ROR

$74

Rotate right $74 through carry

LDA

$73

Load MSBs of +/–read into ACC

STA

$77

Store MSBs in RAM location $77

LDA

$74

Load LSBs of +/–read into ACC

STA

$87

Store LSBs in RAM location $87

BRA

END

Goto end of routine

MINUS:

CLC

Clear carry

ROR

$71

Shift MSBs of –/+ read right

ROR

$72

Shift LSBs of –/+ read right

COM $71

1’s complement of MSBs

COM $72

1’s complement of LSBs

LDA

$72

Load LSBs into ACC

ADD

#$01

Add 1 to LSBs

STA

$72

Store ACC in $72

CLRA

Clear ACC

ADC

$71

Add with carry to MSBs. Result in ACC

STA

$71

Store ACC in $71

STA

$77

Store MSBs in RAM location $77

LDA

$72

Load LSBs in ACC

STA

$87

Store LSBs in RAM location $87

END:

RTS

Return

Load D

IN

word for LTC1090 into ACC

JSR

LDA

STA

LDA

STA

RTS

READ+/–: LDA

JSR

LDA

STA

LDA

STA

RTS

MNEMONIC

DESCRIPTION

LDA

STA

LDA

STA

BSET

JSR

#$50

$0A

#$FF

$06

0, $02

READ–/+

Configuration data for SPCR

Load configuration data into $0A

Configuration data for port C DDR

Load configuration data into port C DDR

Make sure CS is high

Dummy read configures LTC1090 for next

read

Read CH6 with respect to CH7

Read CH7 with respect to CH6

Determines which reading has valid data,

converts to 2’s complement and stores in

RAM

JSR

JSR

JSR

READ+/–

READ–/+

CHK SIGN

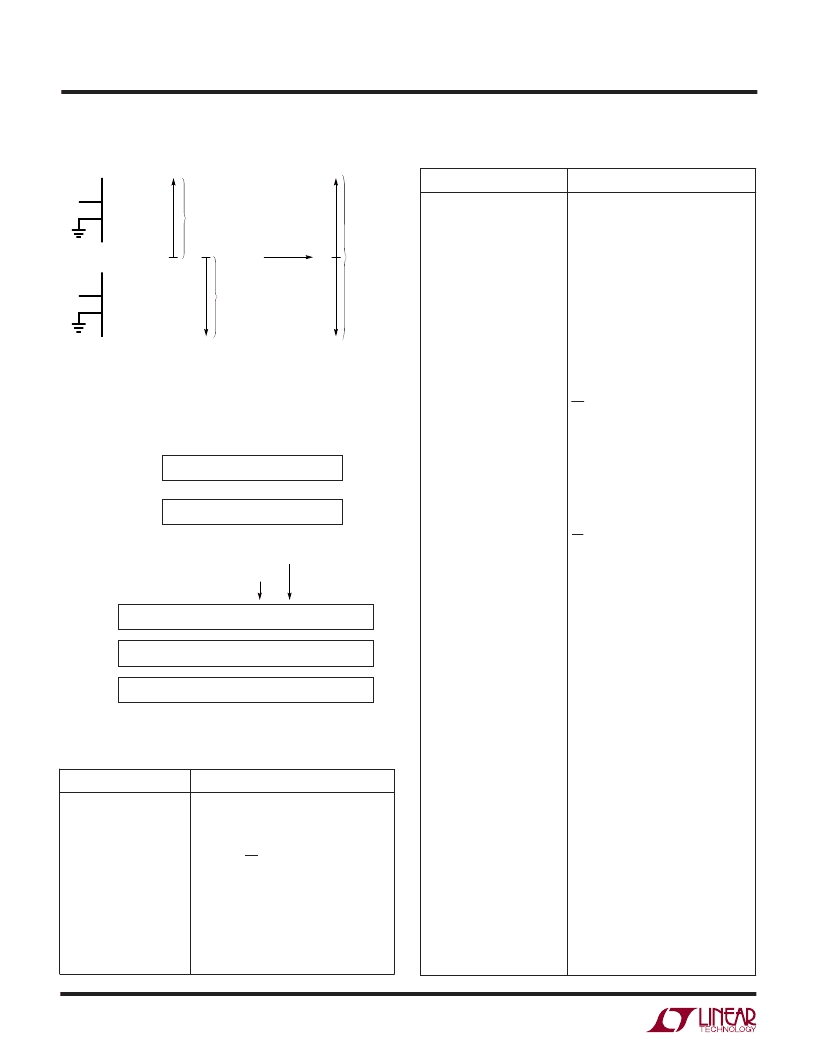

SNEAK-A-BIT

Sneak-A-Bit Code for the LTC1090 Using the MC68HC05C4

LTC1090 TA05

1ST CONVERSION

1ST CONVERSION

1024 STEPS

5V

–5V

5V

–5V

0V

0V

0V

2ND CONVERSION

1024 STEPS

SOFTWARE

2047 STEPS

( + ) CH6

( – ) CH7

V

IN

V

IN

2ND CONVERSION

SNEAK-A-BIT Code

( – ) CH6

( + ) CH7

V

IN

D

OUT

from LTC1090 in MC68HC05C4 RAM

D

IN

words for LTC1090

Location $77

Sign

LSB

B2

B1

B0

B10

B9

B8

filled with 0s

B7

B6

B5

B4

B3

Location $87

(ODD/SIGN)

MUX Addr.

Word

Length

UNI

MSBF

D

IN

1

0

0

1

1

1

1

1

1

D

IN

2

0

1

1

1

1

1

1

1

D

IN

3

0

0

1

1

1

1

1

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LTC1090MJ | Single Chip 10-Bit Data Acquisition System |

| LTC1091AC | 1-, 2-, 6- and 8-Channel, 10-Bit Serial I/O Data Acquisition Systems |

| LTC1091ACN8 | 1-, 2-, 6- and 8-Channel, 10-Bit Serial I/O Data Acquisition Systems |

| LTC1091CN8 | 1-, 2-, 6- and 8-Channel, 10-Bit Serial I/O Data Acquisition Systems |

| LTC1093ACN | 1-, 2-, 6- and 8-Channel, 10-Bit Serial I/O Data Acquisition Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LTC1090MJ | 制造商:LINER 制造商全稱:Linear Technology 功能描述:Single Chip 10-Bit Data Acquisition System |

| LTC1090MJ/883 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Ended Data Acquisition System |

| LTC1091 | 制造商:LINER 制造商全稱:Linear Technology 功能描述:1-, 2-, 6- and 8-Channel, 10-Bit Serial I/O Data Acquisition Systems |

| LTC1091AC | 制造商:LINER 制造商全稱:Linear Technology 功能描述:1-, 2-, 6- and 8-Channel, 10-Bit Serial I/O Data Acquisition Systems |

| LTC1091ACJ8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Ended Data Acquisition System |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。