- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369835 > LRS1806A Flash ROM PDF資料下載

參數(shù)資料

| 型號(hào): | LRS1806A |

| 英文描述: | Flash ROM |

| 中文描述: | 閃存ROM |

| 文件頁(yè)數(shù): | 7/45頁(yè) |

| 文件大小: | 1382K |

| 代理商: | LRS1806A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)

LRS1806A

5

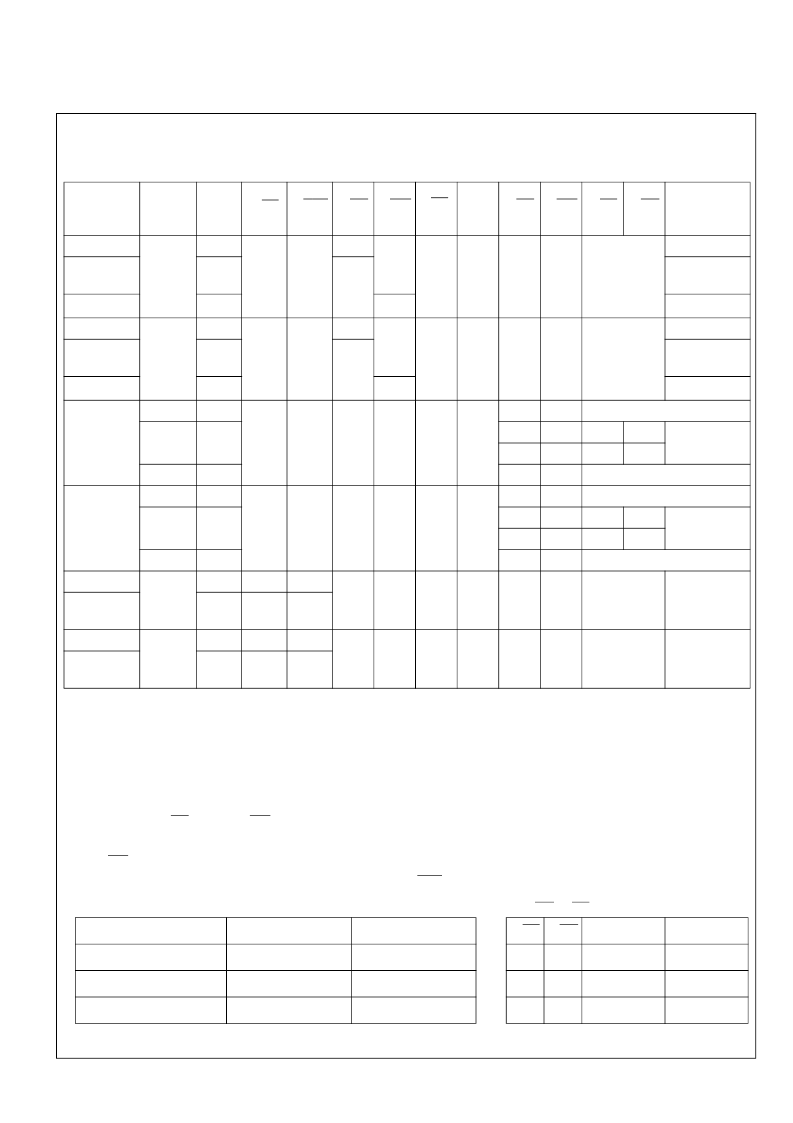

3. Truth Table

3.1 Bus Operation

(1)

Notes:

1. L = V

IL

, H = V

IH

, X = H or L, High-Z = High impedance. Refer to the DC Characteristics.

2. Command writes involving block erase (page buffer) program are reliably executed when F-V

PP

= V

PPH1/2

and F-V

CC

= 2.7V to 3.3

V

.

Command writes involving full chip erase is reliably executed when F-V

PP

= V

PPH1

and F-V

CC

= 2.7V to 3.3

V.

Block erase, full chip erase, (page buffer) program with F-V

PP

< V

PPH1/2

(Min.) produce spurious results and should not

be attempted.

3. Never hold F-OE low and F-WE low at the same timing.

4. Refer Section 5. Command Definitions for Flash Memory valid D

IN

during a write operation.

5. F-WP set to V

IL

or

V

IH

.

6. Electricity consumption of Flash Memory is lowest when F-RST = GND ±0.2V.

7. Flash Read Mode

8. S-UB, S-LB Control Mode

Flash

Smart

combo

RAM

Notes

F-CE

F-RST F-OE F-WE S-CE

1

S-CE

2

S-OE S-WE S-LB S-UB

DQ

0

to DQ

15

Read

Output

Disable

Standby

3,5

L

H

L

H

H

H

X

X

X

(7)

5

H

High - Z

Write

2,3,4,5

L

D

IN

(7)

Read

Sleep

3,5

L

H

L

H

X

L

X

X

X

Output

Disable

5

H

High - Z

Write

2,3,4,5

L

D

IN

Standby

Read

5,6

H

H

X

X

L

H

L

X

H

H

H

H

(8)

Output

Disable

5,6

H

X

H

X

High - Z

Write

Read

5,6

5,6

X

L

X

L

H

H

(8)

(8)

Reset Power

Down

X

L

X

X

L

H

Output

Disable

5,6

H

H

High - Z

H

X

H

L

X

X

Write

5,6

5

(8)

Standby

Standby

H

H

X

X

H

H

X

X

X

High - Z

Reset Power

Down

Standby

Reset Power

Down

5,6

X

L

Sleep

5

H

H

X

X

X

L

X

X

X

High - Z

5,6

X

L

Mode

Address

DQ

0

to DQ

15

S-LB S-UB

DQ

0

to DQ

7

DQ

8

to DQ

15

Read Array

X

D

OUT

L

L

D

OUT

/D

IN

D

OUT

/D

IN

Read Identifier Codes

See 5.2

See 5.2

L

H

D

OUT

/D

IN

High - Z

Read Query

Refer to the Appendix Refer to the Appendix

H

L

High - Z

D

OUT

/D

IN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LRS1808A | Flash ROM |

| LRS1828 | Flash ROM |

| LRS1832 | Flash ROM |

| LRU2642R | Fuse |

| LRU663M | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LRS1806C | 制造商:Sharp Microelectronics Corporation 功能描述:COMBO 4MX16 FLASH + 1MX16 SRAM 3V 72CSP - Trays |

| LRS1808A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Flash ROM |

| LRS1828 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Flash ROM |

| LRS1832 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Flash ROM |

| LRS18AC | 制造商:Sharp Microelectronics Corporation 功能描述:128M Flash Memory with 32M SmartCombo RAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。