- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369797 > LM9822CCWM Signal Conditioner PDF資料下載

參數(shù)資料

| 型號: | LM9822CCWM |

| 英文描述: | Signal Conditioner |

| 中文描述: | 信號調(diào)理 |

| 文件頁數(shù): | 18/20頁 |

| 文件大小: | 245K |

| 代理商: | LM9822CCWM |

Applications Information

(Continued)

(13)

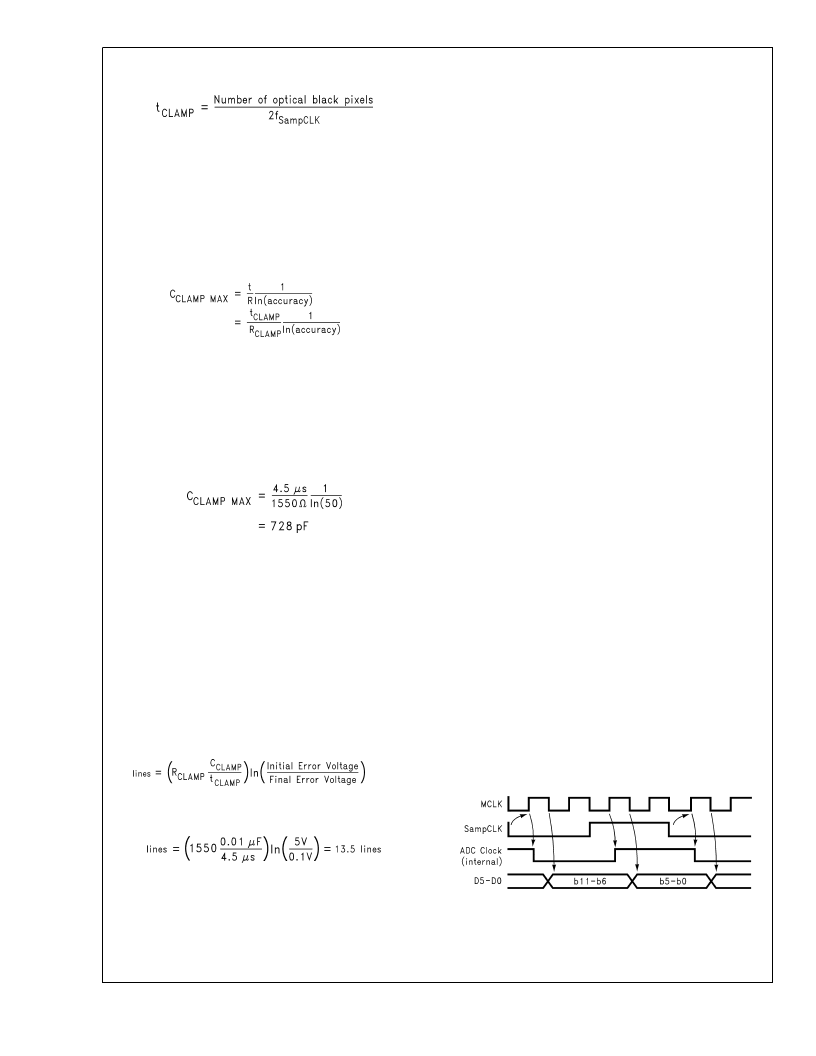

For example, if a sensor has 18 black reference pixels

and f

is 2 MHz with a 50% duty cycle, then t

CLAMP

is 4.5 μs.

The following figure takes the number of optical black

pixels, the amount of time (per pixel) that the clamp is

closed, the sensor’s output impedance, and the desired

accuracy of the final clamp voltage and provides the

maximum clamp capacitor value that allows the clamp

capacitor to settle to the desired accuracy within a single

line:

(14)

Where t

is the amount of time (per line) that the

clamp is on, R

is the output impedance of the CCD

plus 50

for the LM9810/20’s internal clamp switch, and

accuracy is the ratio of the worst-case initial capacitor

voltage to the desired final capacitor voltage. If t

is

4.5 μs, the output impedance of the sensor is 1500

, the

worst case voltage change required across the capacitor

(before the first line) is 5V, and the desired accuracy after

clamping is to within 0.1V (accuracy = 5/0.1 = 50), then:

(15)

The final value for C

CLAMP

should be less than or equal to

C

CLAMP MAX

, but no less than C

CLAMP MIN

.

In some cases, depending primarily on the choice of

sensor, C

CLAMP MAX

may actually be less than C

CLAMP

MIN

, meaning that the capacitor can not be charged to its

final voltage during the black pixels at the beginning of a

line and hold its voltage without drooping for the duration

of that line. This is usually not a problem because in most

applications the sensor is clocked continuously as soon

as power is applied. In this case, a larger capacitor can be

used (guaranteeing that the C

requirement is

met), and the final clamp voltage is forced across the

capacitor over multiple lines. This equation calculates how

many lines are required before the capacitor settles to the

desired accuracy:

(16)

Using the values shown before and a clamp capacitor

value of 0.01 μF, this works out to be:

(17)

In this example, a 0.01 μF capacitor takes 14 lines after

power-up to charge to its final value. On subsequent lines,

the only error will be the droop across a single line which

should be significantly less than the initial error.

If the

LM9810/20 is operating in CDS mode and multiple

lines are used to charge up the clamping capacitors

after power-up, then a clamp capacitor value of 0.01

μF should be significantly greater than the calculated

C

CLAMP MIN

value and can virtually always be used

.

If the LM9810/20 is operating in CIS mode, then signifi-

cantly larger clamp capacitors must be used. Fortunately,

the output impedance of most CIS sensors is significantly

smaller than the output impedance of CCD sensors, and

R

will be dominated by the 50

from the LM9810/

20’s internal clamp switch. With a smaller R

CLAMP

value,

the clamp capacitors will charge faster.

3.0 PERFORMANCE CONSIDERATIONS

3.1 Power Supply

The LM9810/20 should be powered by a single +5V

source. The analog supplies (V

) and the digital supply

(V

) are brought out individually to allow separate bypass-

ing for each supply input. They should not be powered by

two or more different supplies.

In systems with separate analog and digital +5V supplies,

all the supply pins of the LM9810/20 should be powered

by the analog +5V supply. Each supply input should be

bypassed to its respective ground with a 0.1 μF capacitor

located as close as possible to the supply input pin. A

single 10 μF tantalum capacitor should be placed near the

V

A

supply pin to provide low frequency bypassing.

To minimize noise, keep the LM9810/20 and all analog

components as far as possible from noise generators,

such as switching power supplies and high frequency

digital busses. If possible, isolate all the analog compo-

nents and signals (OS, reference inputs and outputs, V

A

,

AGND) on an analog ground plane, separate from the

digital ground plane. The two ground planes should be

tied together at a single point, preferably the point where

the power supply enters the PCB.

3.2 SampCLK Timing

SampCLK is used to time the stages of the LM9810/20’s

sampler, offset DAC and programmable gain amplifier. To

allow for optimum input signal sampling times, SampCLK

may be applied asynchronously to MCLK. The LM9810/

20’s ADC is synchronized with the AFE (including the

sampler, the offset DAC and the PGA) by MCLK.

The LM9810/20’s internal ADC clock is created through a

combination of the applied SampCLK and MCLK signals.

MCLK is used to synchronize the applied SampCLK sig-

nal. The internal ADC clock will go low after the falling

edge of SampCLK is clocked by a rising of MCLK. The

ADC clock will stay low for two MCLK cycles and then go

high. It will stay high until the next falling edge of Samp-

CLK is clocked by MCLK. Figure 11 illustrates this Samp-

CLK, MCLK, and ADC clock timing relationship.

The LM9810/20 is a densely designed, mixed-signal,

monolithic semiconductor. In creating the timing for the

LM9810/20, it must be considered that internal events,

DS100943-83

FIGURE 11. LM9810/20 Relative Event Timing

L

www.national.com

18

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM9822CCWMX | Signal Conditioner |

| LM9823 | |

| LMA110 | .5-6 GHz MESFET Amplifier |

| LMA110A | .5-6 GHz MESFET Amplifier |

| LMA110B | .5-8GHz MESFET Amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM9822CCWM/NOPB | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| LM9822CCWM1 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LM9822 3 Channel 42-Bit Color Scanner Analog Front End |

| LM9822CCWMX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Signal Conditioner |

| LM9822CCWMX/NOPB | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| LM9822CCWMX2 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:LM9822 3 Channel 42-Bit Color Scanner Analog Front End |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。