- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358816 > LM2324TMX (NATIONAL SEMICONDUCTOR CORP) PLLatinum⑩ 2.0 GHz Frequency Synthesizer for RF Personal Communications PDF資料下載

參數(shù)資料

| 型號(hào): | LM2324TMX |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | PLLatinum⑩ 2.0 GHz Frequency Synthesizer for RF Personal Communications |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO16 |

| 封裝: | TSSOP-16 |

| 文件頁數(shù): | 7/12頁 |

| 文件大小: | 157K |

| 代理商: | LM2324TMX |

2.0 Programming Description

(Continued)

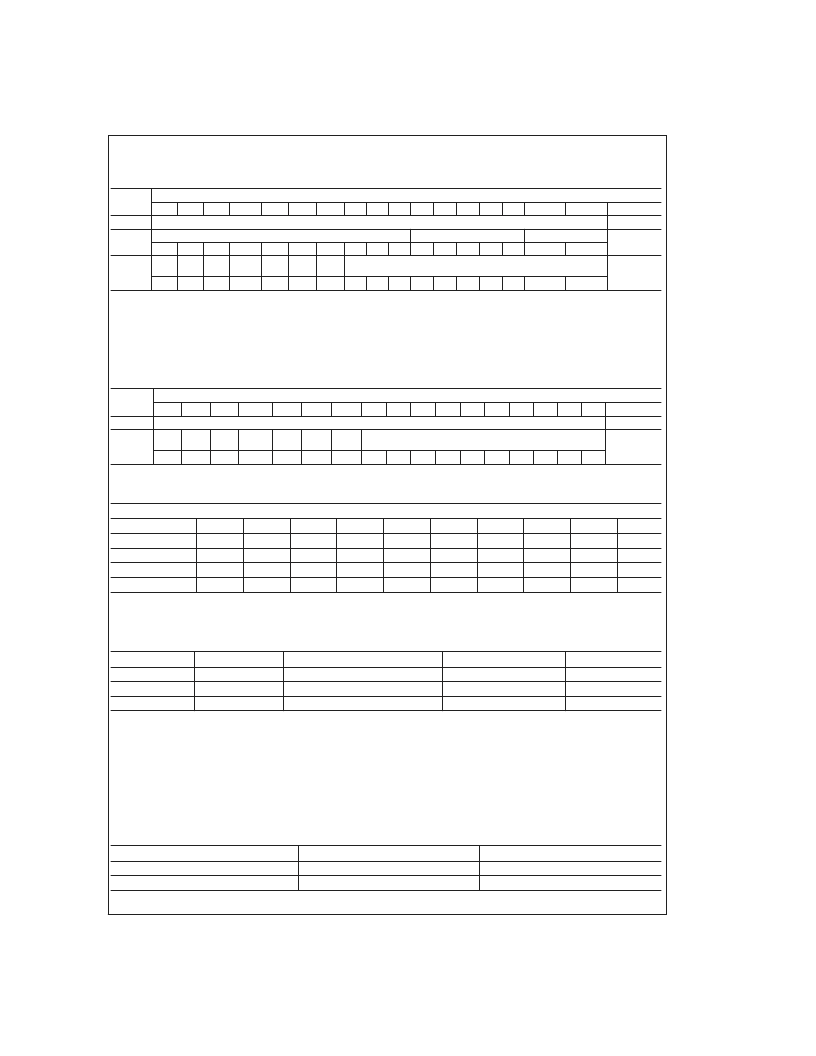

2.1.2 Register Content Truth Table

MSB

17

SHIFT REGISTER BIT LOCATION

11

10

9

Data Field

LSB

16

15

14

13

12

8

7

6

5

4

3

2

1

0

Register

ADDR Field

N

NB_CNTR[9:0]

N12

TEST

RS

NA_CNTR[4:0]

N5

R_CNTR[9:0]

CTL_WORD[1:0]

N1

0

N16

X

N15

X

N14

X

N13

N11

PD_

POL

R11

N10

CP_

TRI

R10

N9

N8

N7

N6

N3

N2

N0

R

1

R16

R15

R14

R13

R12

R9

R8

R7

R6

R5

R4

R3

R2

R1

R0

2.2 R REGISTER

If the Address Bit (ADDR) is 1, when LE is transitioned high data is transferred from the 18-bit shift register into the 14-bit R reg-

ister. The R register contains a latch which sets the PLL 10-bit R counter divide ratio. The divide ratio is programmed using the

bits R_CNTR as shown in table 2.2.1. The ratio must be

≥

2. The PD_POL, CP_TRI and TEST bits control the phase detector po-

larity, charge pump TRI-STATE, and test mode respectively, as shown in 2.2.2. The RS bit is reserved and should always be set

to zero. X denotes a don’t care condition. Data is clocked into the shift register MSB first.

MSB

17

SHIFT REGISTER BIT LOCATION

11

10

9

Data Field

CP_

TRI

R10

R9

R8

LSB

16

15

14

13

12

8

7

6

5

4

3

2

1

0

Register

ADDR Field

R

X

X

X

TEST

RS

PD_

POL

R11

R_CNTR[9:0]

1

R16

R15

R14

R13

R12

R7

R6

R5

R4

R3

R2

R1

R0

2.2.1 10-Bit Programmable Reference Divider Ratio (R Counter)

R_CNTR[9:0]

R6

0

0

1

Divide Ratio

2

3

1,023

R9

0

0

1

R8

0

0

1

R7

0

0

1

R5

0

0

1

R4

0

0

1

R3

0

0

1

R2

0

0

1

R1

1

1

1

R0

0

1

1

Notes:

Divide ratio: 2 to 1,023 (Divide ratios less than 2 are prohibited)

R_CNTR — These bits select the divide ratio of the programmable reference dividers.

2.2.2 R Register Truth Table

Bit

Location

R[10]

R[11]

R[13]

Function

0

1

CP_TRI

PD_POL

TEST

Charge Pump TRI-STATE

Phase Detector Polarity

Test Mode Bit

Normal Operation

Negative

Normal Operation

TRI-STATE

Positive

Test Mode

If the test mode is NOT activated (R[13]=0), the charge pump is active when CP_TRI is set LOW. When CP_TRI is set HIGH, the

charge pump output and phase comparator are forced to a TRI-STATE condition. This bit must be set HIGH if the test mode is

ACTIVATED (R[13]=1).

If the test mode is NOT activated (R[13]=0), PD_POL sets the VCO characteristics to positive when set HIGH. When PD_POL

is set LOW, the VCO exhibits a negative characteristic where the VCO frequency decreases with increasing control voltage.

If the test mode is ACTIVATED (R[13]=1), the outputs of the N and R counters are directed to the CP

o

output to allow for testing.

The PD_POL bit selects which counter output according to Table 2.2.3.

2.2.3 Test Mode Truth Table (R[13] = 1)

CP

o

Output

R Divider Output

N Divider Output

CP_TRI R[10]

1

1

PD_POL R[11]

0

1

L

www.national.com

7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM234Z-3 | 3-Terminal Adjustable Current Sources |

| LM234Z | CAP FILM MKP 1UF 440VAC X1 20% |

| LM234D | THREE TERMINAL ADJUSTABLE CURRENT SOURCES |

| LM234Z-6 | LED 2MM QUAD GREEN |

| LM236 | 2.5-V INTEGRATED REFERENCE CIRCUITS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM2326 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum⑩ Low Power Frequency Synthesizer for RF Personal Communications |

| LM2326SLBX | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum⑩ Low Power Frequency Synthesizer for RF Personal Communications |

| LM233-155.52M | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:5.0x7.0mm Surface Mount LVDS Clock Oscillator Series |

| LM2332-9 | 制造商:Power-One 功能描述:100W, AC/DC, RUGGED - Bulk |

| LM2335 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PLLatinum⑩ Low Power Dual Frequency Synthesizer for RF Personal Communications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。