- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358798 > LH543620 (Sharp Corporation) 1024 x 36 Synchronous FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | LH543620 |

| 廠商: | Sharp Corporation |

| 英文描述: | 1024 x 36 Synchronous FIFO |

| 中文描述: | 1024 × 36同步FIFO |

| 文件頁數(shù): | 10/38頁 |

| 文件大?。?/td> | 269K |

| 代理商: | LH543620 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

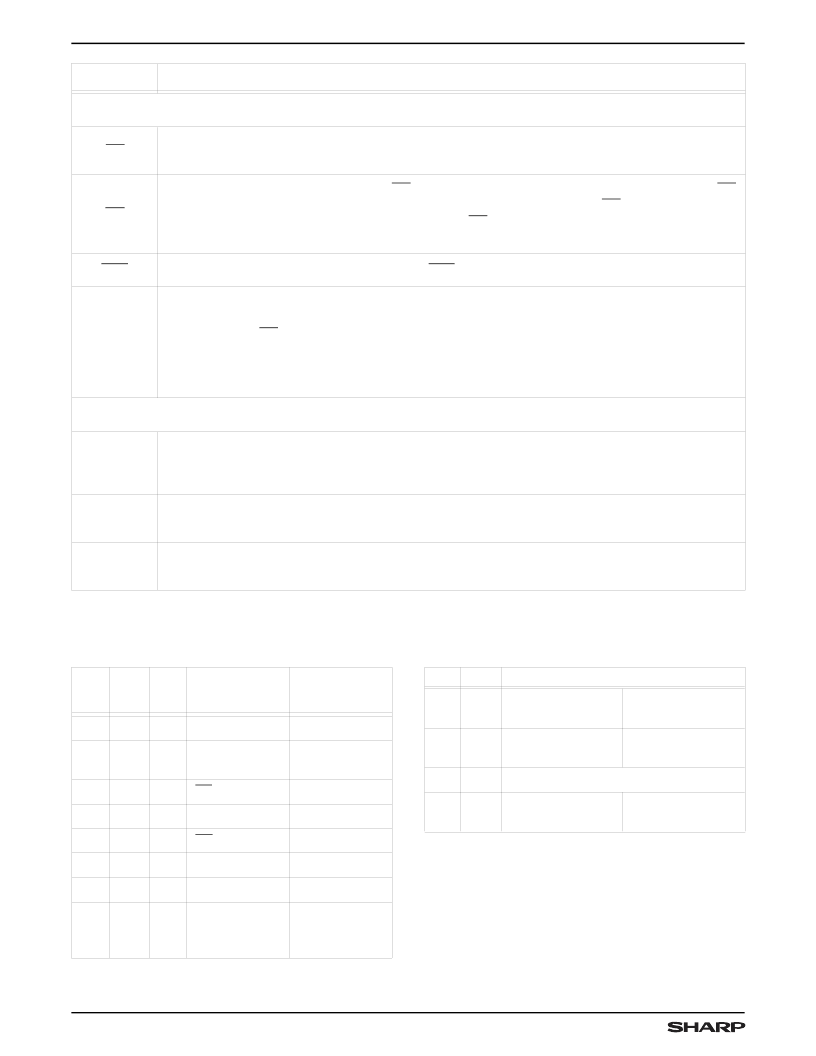

Table 1. Input-Port Address

ADI

2

ADI

1

ADI

0

SELECTION

DEFAULT VALUE

(of the selected

REGISTER)

L

L

L

RBASE register

0

L

L

H

ROFFSET

register

0

L

H

L

AF offset value

8

L

H

H

Parity register

0

H

L

L

AE offset value

8

H

L

H

Control register

1

H

H

L

Mailbox

0

H

H

H

Resource

registers write

disabled

Table 2. Input-Port Word-Width Selection

WSI

1

WSI

0

FUNCTION

L

L

9-Bit Data-Path

Width

Input data D[8:0]

L

H

18-Bit Data-Path

Width

Input data D[17:0]

H

L

Reserved

H

H

36-Bit Data-Path

Width

Input data D[35:0]

PIN NAME

DESCRIPTION

ASYNCHRONOUS CONTROL

RS

Master Reset.

When asserted LOW, the LH543620 internal resource registers are set to their

default value. See Table 1. The status flags indicate Empty FIFO.

OE

Output Enable.

When asserted LOW, OE forces Q[35:0] to be active. When deasserted HIGH, OE

forces Q[35:0] into a Hi-Z state. Bit 6 of the control register governs whether OE suppresses the

advancement of the Read Pointer (RP). In this case, OE must obey setup time and hold time

relative to CKO.

BYE

Data-Bypass Enable.

When asserted LOW, BYE connects Q[35:0] directly to D[35:0].

CAPR

Command-Address Port Reference.

CAPR determines the source of the 16-bit word to be loaded

into the resource register. Whenever CAPR is LOW, the word comes from the Input Port. Whenever

CAPR is HIGH (OE is HIGH), the word comes from the Output Port.

NOTES

:

1. The destination of the resource register is always the Output Port.

2. CAPR is assumed to be a steady signal. It is not allowed to change ‘on-the-fly’ during operation.

CONTROL SIGNALS SYNCHRONOUS TO THE INPUT CLOCK

ENI

1

, ENI

2

Input-Port Enables.

ENI

1

and ENI

2

are active HIGH and synchronous to the rising edge of CKI.

Data is written into the FIFO memory array when both ENI

1

and ENI

2

are asserted HIGH.

NOTE:

ENI

1

, ENI

2

DO NOT ENABLE writing data into the Resource Registers or the Mailbox.

ADI[2:0]

Input-Port Address.

ADI[2:0] specifies the Input-Port destination. See Table 1. ADI[2:0] is

synchronized to the rising edge of CKI.

WSI[1:0]

Input-Port Word-Width Selection.

WSI[1:0] selects the Input-Port Word-Width. See Table 2.

WSI[1:0] is synchronous to the rising edge of CKI.

LH543620

1024

×

36 Synchronous FIFO

10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH5464-NR | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5464-Q | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5464-P | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5464-N | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

| LH5464-MQ | 5 mm T1 3/4 LED, Diffused Super-Bright, Hyper-Red GaAIAs-LED |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH543620M-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous FIFO |

| LH543620M-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous FIFO |

| LH543620M-30 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous FIFO |

| LH543620P-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous FIFO |

| LH543620P-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x36 Synchronous FIFO |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。