- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377639 > LFX1200B-4F900I (Lattice Semiconductor Corporation) The ispXPGA architecture PDF資料下載

參數(shù)資料

| 型號(hào): | LFX1200B-4F900I |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | The ispXPGA architecture |

| 中文描述: | 在ispXPGA架構(gòu) |

| 文件頁數(shù): | 18/89頁 |

| 文件大?。?/td> | 941K |

| 代理商: | LFX1200B-4F900I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

Lattice Semiconductor

ispXPGA Family Data Sheet

18

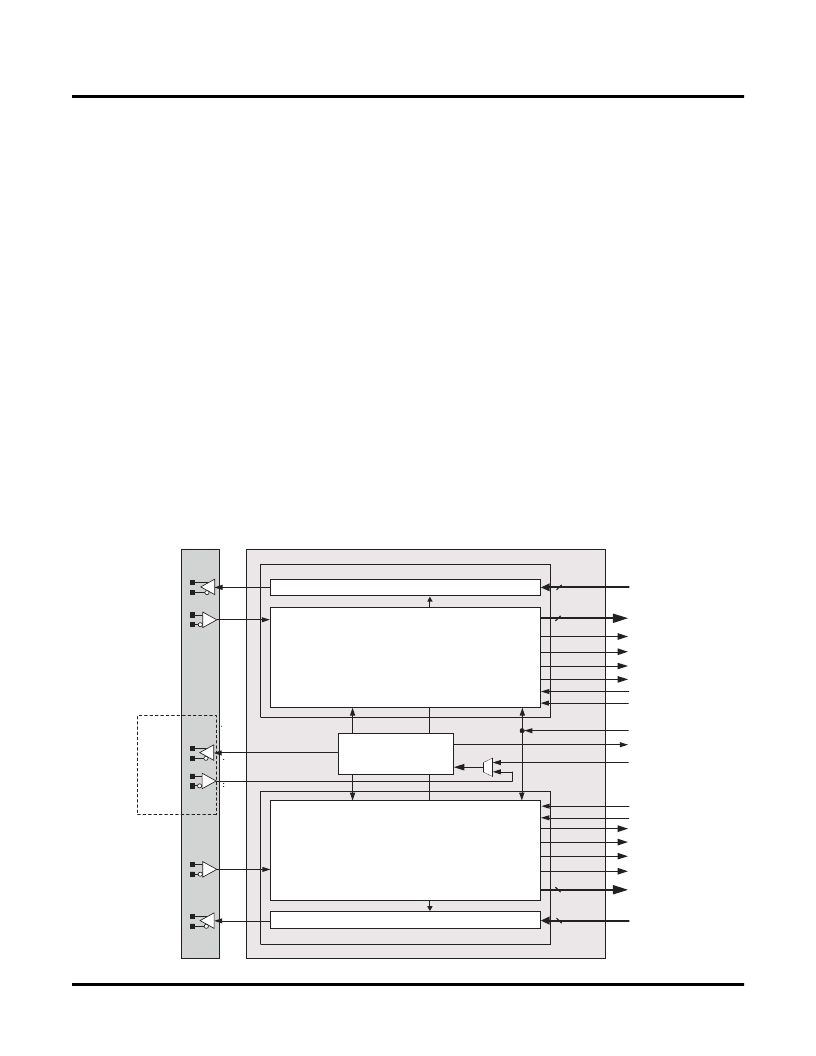

High Speed Serial Interface Block (sysHSI Block)

The High Speed Serial Interface (sysHSI) allows high speed serial data transfer over a pair of LVDS I/O. The

ispXPGA devices have multiple sysHSI blocks.

Each sysHSI block has two SERDES blocks which contain two main sub-blocks, Transmitter (with a serializer) and

Receiver (with a deserializer) including Clock/Data Recovery Circuit (CDR). Each SERDES can be used as a full

duplex channel. The two SERDES in sysHSI blocks share a common clock and must operate at the same nominal

frequency. Figure 20 shows the sysHSI block.

Device features support two data coding modes: 10B/12B and 8B/10B (for use with other encoding schemes, see

Lattice’s sysHSI technical notes). The encoding and decoding of the 10B/12B standard are performed within the

sysHSI block. For the 8B/10B standard, the symbol boundaries are aligned internally but the encoding and decod-

ing are performed outside the sysHSI block.

Each SERDES block receives a single high speed serial data input stream (with embedded clock) from an input,

and provide a low speed 10-bit wide data stream and a recovered clock to the device. For transmitting, SERDES

converts a 10-bit wide low-speed data stream to a single high-speed data stream with embedded clock for output.

Additionally, multiple sysHSI blocks can be grouped together to form a source synchronous interface of 1-10 chan-

nels.

Table 7 shows the clock sources available for the REFCLKs of the different sysHSI blocks. The Signal Description

table in this data sheet provides the descriptions of the sysHSI block inputs and outputs.

For more information on the SERDES/CDR, refer to Lattice technical note number TN1020,

sysHSI Usage Guide-

lines

.

Figure 20. sysHSI Block Diagram

S

S

M

REFCLK

SOUT

SIN

SS_CLKOUT

SS_CLKIN

SERDES(HSI#A)

Serializer

CAL

CSLOCK

SERDES(HSI#B)

SOUT

SIN

LOSS

TXD

RXD

RECCLK

SYDT

EXLOSS

CDRLOCK

10

10

TXD

RXD

RECCLK

SYDT

LOSS

CDRLOCK

10

10

To PICs

To PICs

To PICs

To PICs

To PICs

From PICs

From PICs

To PICs

To PICs

To PICs

To PICs

To PICs

From PICs

From PICs

From Global

Clock Tree

sysIO

From PICs

To PICs

CDRRST

CDRRST

EXLOSS

From PICs

From PICs

Deserializer and Clock/Data Recovery

CSPLL

Serializer

Deserializer and Clock/Data Recovery

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFX1200C-4F900I | The ispXPGA architecture |

| LFX125C-3F900I | The ispXPGA architecture |

| LFX125C-4F900I | The ispXPGA architecture |

| LFX200B-3F900I | The ispXPGA architecture |

| LFX1200B-03F900C | The ispXPGA architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LFX1200B-4FE680C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX1200B-4FE680I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX1200B-4FH516C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX1200B-4FH516I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX1200B-4FN256C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。