- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377639 > LFX1200B-3F900C (Lattice Semiconductor Corporation) The ispXPGA architecture PDF資料下載

參數(shù)資料

| 型號(hào): | LFX1200B-3F900C |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | The ispXPGA architecture |

| 中文描述: | 在ispXPGA架構(gòu) |

| 文件頁(yè)數(shù): | 27/89頁(yè) |

| 文件大?。?/td> | 941K |

| 代理商: | LFX1200B-3F900C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)

Lattice Semiconductor

ispXPGA Family Data Sheet

27

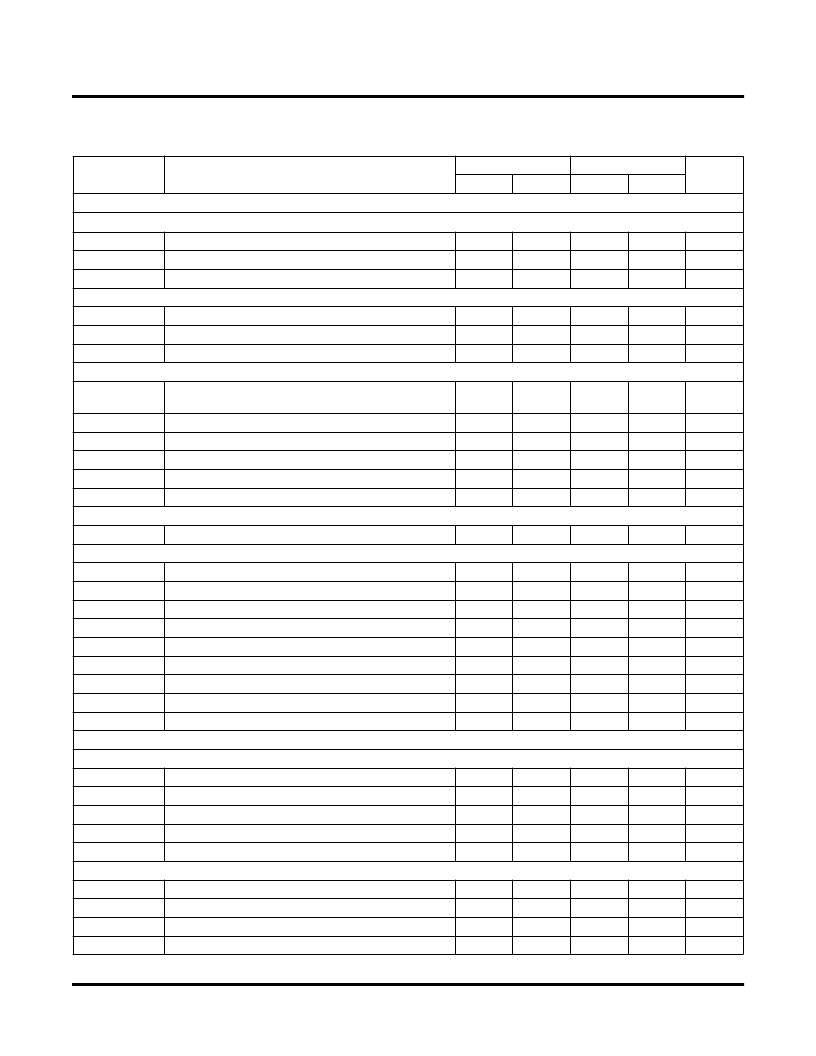

ispXPGA PFU Timing Parameters

Over Recommended Operating Conditions

Parameter

Description

-4

-3

Units

Min.

Max.

Min.

Max.

Functional Delays

LUTs

t

LUT4

t

LUT5

t

LUT6

Shift Register (LUT)

4-Input LUT Delay

—

0.44

—

0.51

ns

5-Input LUT Delay

—

0.79

—

0.91

ns

6-Input LUT Delay

—

0.93

—

1.07

ns

t

LSR_S

t

LSR_H

t

LSR_CO

Arithmetic Functions

Shift Register Setup Time

-0.62

—

-0.53

—

ns

Shift Register Hold Time

0.63

—

0.72

—

ns

Shift Register Clock to Output Delay

—

0.75

—

0.86

ns

t

LCTHRUR

MC (Macro Cell) Carry In to MC Carry Out Delay (Rip-

ple)

—

0.09

—

0.10

ns

t

LCTHRUL

t

LSTHRU

t

LSINCOUT

t

LCINSOUTR

t

LCINSOUTL

Feed-thru

1

MC Carry In to MC Carry Out Delay (Look Ahead)

—

0.05

—

0.06

ns

MC Sum In to MC Sum Out Delay

—

0.45

—

0.52

ns

MC Sum In to MC Carry Out Delay

—

0.31

—

0.36

ns

MC Carry In to MC Sum Out Delay (Ripple)

—

0.39

—

0.45

ns

MC Carry In to MC Sum Out Delay (Look Ahead)

—

0.28

—

0.32

ns

t

LFT

Distributed RAM

PFU Feed-Thru Delay

—

0.16

—

0.18

ns

t

LRAM_CO

t

LRAMAD_S

t

LRAMD_S

t

LRAMWE_S

t

LRAMAD_H

t

LRAMD_H

t

LRAMWE_H

t

LRAMCPW

t

LRAMADO

Register/Latch Delays

Registers

Clock to RAM Output

—

1.33

—

1.53

ns

Address Setup Time

-0.40

—

-0.34

—

ns

Data Setup Time

0.22

—

0.25

—

ns

Write Enable Setup Time

0.46

—

0.53

—

ns

Address Hold Time

0.60

—

0.69

—

ns

Data Hold Time

0.11

—

0.13

—

ns

Write Enable Hold Time

0.12

—

0.14

—

ns

Clock Pulse Width (High or Low)

3.00

—

3.45

—

ns

Address to Output Delay

—

0.93

—

1.07

ns

t

L_CO

t

L_S

t

L_H

t

LCE_S

t

LCE_H

Latches

Register Clock to Output Delay

—

0.62

—

0.71

ns

Register Setup Time (Data before Clock)

0.14

—

0.16

—

ns

Register Hold Time (Data after Clock)

-0.12

—

-0.10

—

ns

Register Clock Enable Setup Time

-0.11

—

-0.09

—

ns

Register Clock Enable Hold Time

0.11

—

0.13

—

ns

t

L_GO

t

LL_S

t

LL_H

t

LLPD

Latch Gate to Output Delay

—

0.10

—

0.12

ns

Latch Setup Time

0.14

—

0.16

—

ns

Latch Hold Time

-0.12

—

-0.10

—

ns

Latch Propagation Delay (Transparent Mode)

—

0.10

—

0.12

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFX1200B-03F900I | The ispXPGA architecture |

| LFX1200B-04F900C | The ispXPGA architecture |

| LFX1200C-4F900C | The ispXPGA architecture |

| LFX125B-4F900C | The ispXPGA architecture |

| LFX200B-4F900C | The ispXPGA architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LFX1200B-3F900I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:The ispXPGA architecture |

| LFX1200B-3FE680C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX1200B-3FE680I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX1200B-3FH516C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

| LFX1200B-3FH516I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:ispXPGA Family |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。