- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377639 > LFX1200B-04F900C (LATTICE SEMICONDUCTOR CORP) The ispXPGA architecture PDF資料下載

參數(shù)資料

| 型號: | LFX1200B-04F900C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | The ispXPGA architecture |

| 中文描述: | FPGA, 3844 CLBS, 1250000 GATES, PBGA900 |

| 封裝: | FPBGA-900 |

| 文件頁數(shù): | 29/89頁 |

| 文件大小: | 941K |

| 代理商: | LFX1200B-04F900C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

Lattice Semiconductor

ispXPGA Family Data Sheet

29

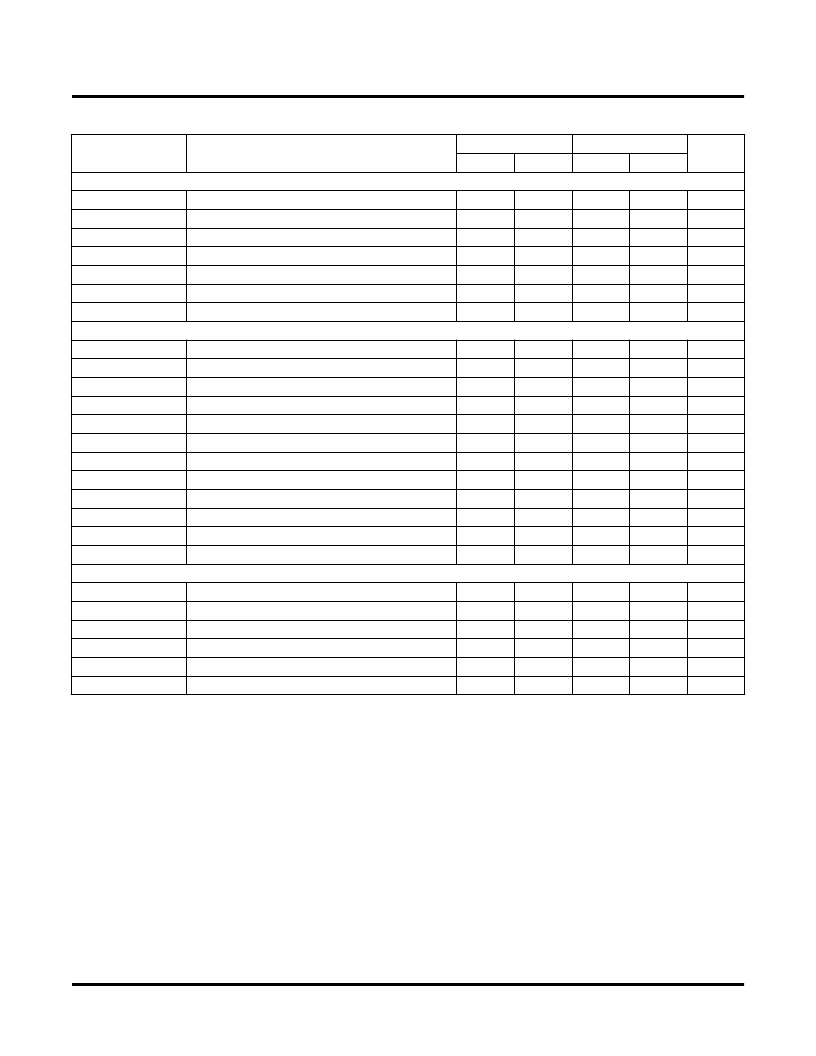

ispXPGA EBR Timing Parameters

Parameter

Description

-4

-3

Units

Min.

Max.

Min.

Max.

Synchronous Write

t

EBSWAD_S

t

EBSWAD_H

t

EBSWCPW

t

EBSWWE_S

t

EBSWWE_H

t

EBSWD_S

t

EBSWD_H

Synchronous Read

Address Setup Delay

0.61

—

0.70

—

ns

Address Hold Delay

-0.39

—

-0.33

—

ns

Clock Pulse Width

—

3.40

—

3.91

ns

Write Enable Setup Time

-0.12

—

-0.10

—

ns

Write Enable Hold Time

0.16

—

0.18

—

ns

Data Setup Time

0.28

—

0.32

—

ns

Data Hold Time

-0.26

—

-0.22

—

ns

t

EBSR_CO

t

EBSRAD_S

t

EBSRAD_H

t

EBSRCPW

t

EBSRCE_S

t

EBSRCE_H

t

EBSRWE_S

t

EBSRWE_H

t

EBSRWEEN

t

EBSRWEDIS

t

EBSREN

t

EBSRDIS

Asynchronous Read

Clock to Data Delay

—

2.19

—

2.52

ns

Address Setup Delay

0.10

—

0.12

—

ns

Address Hold Delay

-0.07

—

-0.06

—

ns

Clock Pulse Width

—

3.40

—

3.91

ns

Clock Enable Setup Time

-1.71

—

-1.45

—

ns

Clock Enable Hold Time

1.69

—

1.94

—

ns

Write Enable Setup Time

-0.17

—

-0.14

—

ns

Write Enable Hold Time

0.12

—

0.14

—

ns

Write Enable to Data Enable Time

—

1.05

—

1.21

ns

Write Enable to Data Disable Time

—

1.02

—

1.17

ns

Output Enable to Data Enable Time

—

1.05

—

1.21

ns

Output Enable to Data Disable Time

—

0.86

—

0.99

ns

t

EBARADO

t

EBARAD_H

t

EBARWEEN

t

EBARWEDIS

t

EBAREN

t

EBARDIS

Address to New Valid Data Delay

—

2.46

—

2.83

ns

Address to Previous Valid Data Delay

—

2.17

—

2.50

ns

Write Enable to Data Enable Time

—

1.04

—

1.20

ns

Write Enable to Data Disable Time

—

1.01

—

1.16

ns

Output Enable to Data Enable Time

—

1.05

—

1.21

ns

Output Enable to Data Disable Time

—

0.86

—

0.99

ns

Timing v.2.0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFX1200C-4F900C | The ispXPGA architecture |

| LFX125B-4F900C | The ispXPGA architecture |

| LFX200B-4F900C | The ispXPGA architecture |

| LFX500B-4F900C | The ispXPGA architecture |

| LFX1200B-4F900C | The ispXPGA architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LFX1200B-04FE680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200B-04FEN680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 1.25M Gt ispJTAG 2. 5/3.3V -4 Spd RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200B-04FEN680C2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200B-05F900C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| LFX1200B-05FE680C | 功能描述:FPGA - 現(xiàn)場可編程門陣列 15376 LUT-4 496 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。