- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377634 > LFECP15E-5F484C (LATTICE SEMICONDUCTOR CORP) 12-Bit 66 kSPS ADC Ser. Out, Pgrmable MSB/LSB First, Pgrmable Power Down/Output Data Length, 11 Ch. 20-PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | LFECP15E-5F484C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | 12-Bit 66 kSPS ADC Ser. Out, Pgrmable MSB/LSB First, Pgrmable Power Down/Output Data Length, 11 Ch. 20-PLCC |

| 中文描述: | FPGA, 1920 CLBS, 15400 GATES, 420 MHz, PBGA484 |

| 封裝: | 23 X 23 MM, FPBGA-484 |

| 文件頁數(shù): | 59/117頁 |

| 文件大小: | 557K |

| 代理商: | LFECP15E-5F484C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁當(dāng)前第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁

3-23

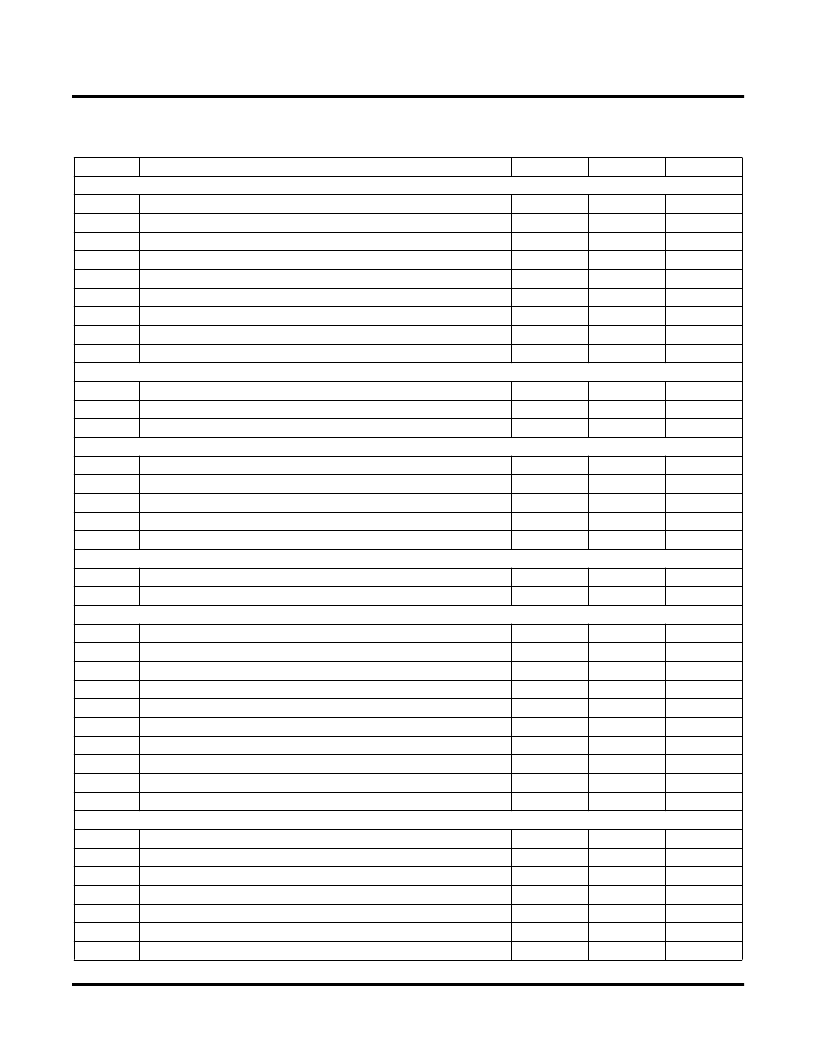

DC and Switching Characteristics

LatticeECP/EC Family Data Sheet

Lattice Semiconductor

LatticeECP/EC sysCONFIG Port Timing Speci

fi

cations

Over Recommended Operating Conditions

Parameter

sysCONFIG Byte Data Flow

t

SUCBDI

Byte D[0:7] Setup Time to CCLK

t

HCBDI

Byte D[0:7] Hold Time to CCLK

t

CODO

Clock to Dout in Flowthrough Mode

t

SUCS

CS[0:1] Setup Time to CCLK

t

HCS

CS[0:1] Hold Time to CCLK

t

SUWD

Write Signal Setup Time to CCLK

t

HWD

Write Signal Hold Time to CCLK

t

DCB

CCLK to BUSY Delay Time

t

CORD

Clock to out for read Data

sysCONFIG Byte Slave Clocking

t

BSCH

Byte Slave Clock Minimum High Pulse

t

BSCL

Byte Slave Clock Minimum Low Pulse

t

BSCYC

Byte Slave Clock Cycle Time

sysCONFIG Serial (Bit) Data Flow

t

SUSCDI

Din Setup Time to CCLK Slave Mode

t

HSCDI

Din Hold Time to CCLK Slave Mode

t

CODO

Clock to Dout in Flowthrough Mode

t

SUMCDI

Din Setup Time to CCLK Master Mode

t

HMCDI

Din Hold Time to CCLK Master Mode

sysCONFIG Serial Slave Clocking

t

SSCH

Serial Slave Clock Minimum High Pulse

t

SSCL

Serial Slave Clock Minimum Low Pulse

sysCONFIG POR, Initialization and Wake Up

t

ICFG

Minimum Vcc to INIT High

t

VMC

Time from t

ICFG

to valid Master Clock

t

PRGMRJ

PROGRAMB Pin Pulse Rejection

t

PRGM

PROGRAMB Low Time to Start Con

fi

guration

t

DINIT

PROGRAMB High to INIT High Delay

t

DPPINIT

Delay Time from PROGRAMB Low to INIT Low

t

DPPDONE

Delay Time from PROGRAMB Low to DONE Low

t

IODISS

User I/O Disable from PROGRAMB Low

t

IOENSS

User I/O Enabled Time from CCLK Edge During Wake-up Sequence

t

MWC

Additional Wake Master Clock Signals after Done Pin High

sysCONFIG SPI Port

t

CFGX

Init High to CCLK Low

t

CSSPI

Init High to CSSPIN Low

t

CSCCLK

CCLK Low before CSSPIN Low

t

SOCDO

CCLK Low to Output Valid

t

SOE

CSSPIN Active Setup Time

t

CSPID

CSSPIN Low to First Clock Edge Setup Time

f

MAXSPI

Max Frequency for SPI

Description

Min

Max

Units

7

1

—

7

1

7

1

—

—

—

—

ns

ns

ns

ns

ns

ns

ns

ns

ns

TBD

—

—

—

—

12

12

6

6

15

—

—

—

ns

ns

ns

7

1

—

7

1

—

—

12

—

—

ns

ns

ns

ns

ns

6

6

—

—

ns

ns

—

—

—

25

—

—

—

—

—

120

50

2

10

—

1

37

37

25

25

—

ms

us

ns

ns

ms

ns

ns

ns

ns

cycles

—

—

0

—

300

1

2

-

15

—

μs

us

ns

ns

ns

ns

MHz

300+3cyc

—

600+6cyc

20

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFECP15E-5F484I | LatticeECP/EC Family Data Sheet |

| LFECP15E-5F672I | LatticeECP/EC Family Data Sheet |

| LFECP15E-5F900I | 12-Bit 66 kSPS ADC Ser. Out, Pgrmable MSB/LSB First, Pgrmable Power Down/Output Data Length, 11 Ch. 20-PDIP |

| LFECP15E-5Q208I | LatticeECP/EC Family Data Sheet |

| LFECP15E-5T100C | Enhanced Product 12-Bit Analog-To-Digital Converter W/ Serial Control And 11 Analog Input 20-SSOP -55 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LFECP15E-5F484I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

| LFECP15E-5F672C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

| LFECP15E-5F672I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

| LFECP15E-5F900C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

| LFECP15E-5F900I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeECP/EC Family Data Sheet |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。