- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377624 > LF3338 (Logic Devices Incorporated) 8-Bit Vertical Digital Image Filter(8位垂直數(shù)字圖像濾波器) PDF資料下載

參數(shù)資料

| 型號: | LF3338 |

| 廠商: | Logic Devices Incorporated |

| 英文描述: | 8-Bit Vertical Digital Image Filter(8位垂直數(shù)字圖像濾波器) |

| 中文描述: | 8位垂直數(shù)字圖像過濾器(8位垂直數(shù)字圖像濾波器) |

| 文件頁數(shù): | 6/15頁 |

| 文件大小: | 303K |

| 代理商: | LF3338 |

DEVICES INCORPORATED

LF3338

8-Bit Vertical Digital Image Filter

6

Video Imaging Products

04/06/1999–LDS.3338-B

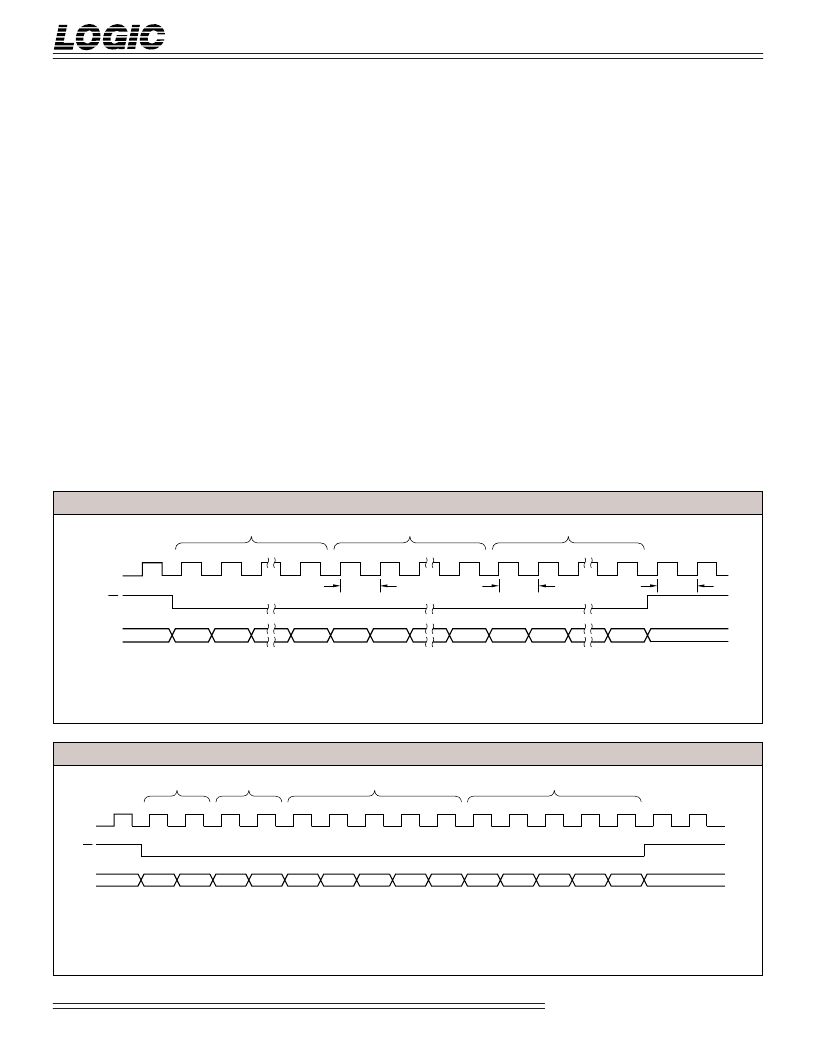

F

IGURE

7. C

ONFIGURATION

/C

ONTROL

R

EGISTER

L

OADING

S

EQUENCE

ADDR

1

DATA

1

ADDR

3

DATA

4

CONFIG REG

ROUND REGISTER

LIMIT REGISTER

CLK

LD

CF

11-0

W2

W1: Configuration Register loaded with new data on this rising clock edge.

W2: Select Register loaded with new data on this rising clock edge.

W3: Round Register loaded with new data on this rising clock edge.

W4: Limit Register loaded with new data on this rising clock edge.

W3

W4

DATA

1

DATA

3

DATA

2

ADDR

4

DATA

2

DATA

1

SELECT REG

ADDR

2

DATA

1

W1

DATA

4

DATA

3

3 set to “0”. Any LF3338s cascaded

after the first LF3338 should have

Bit 0 of Configuration Register 3 set

to “1”. When not cascading, Bit 0 of

Configuration Register 3 should be

set to “0”.

It is important to note that the first

multiplier on all cascaded devices

should not be used. This is because

the first multiplier does not have a

line buffer in front of it. The coeffi-

cient value sent to the first multi-

plier on a cascaded device should be

“0”.

Rounding

The filter output may be rounded by

adding the contents of one of the

sixteen round registers to the filter

output (see Figure 4). Each round

register is 32 bits wide and user-

programmable. This allows the filter’s

output to be rounded to any precision

required. Since any 32-bit value may

be programmed into the round

registers, the device can support

complex rounding algorithms as well

as standard half-LSB rounding. RSL

3-0

determines which of the sixteen round

registers are used in the rounding

operation. A value of 0 on RSL

3-0

selects round register 0. A value of 1

selects round register 1 and so on.

RSL

3-0

may be changed every clock

cycle if desired. This allows the

rounding algorithm to be changed

every clock cycle. This is useful when

filtering interleaved data. If rounding

is not desired, a round register should

be loaded with 0 and selected as the

register used for rounding. Round

register loading is discussed in the

LF Interface

TM

section.

Output Select

The word width of the filter output

is 32 bits. However, only 16 bits

may be sent to DOUT

15-0

. The select

circuitry determines which 16 bits

are passed (see Table 1). There are

sixteen select registers which control

the select circuitry. Each select

register is 5 bits wide and user-

programmable. RSL

3-0

determines

which of the sixteen select registers

are used in the select circuitry.

Select register 0 is chosen by loading

a 0 on RSL

3-0

. Select register 1 is

chosen by loading a 1 on RSL

3-0

and

so on. RSL

3-0

may be changed every

clock cycle if desired. This allows

the 16-bit window to be changed

every clock cycle. This is useful

when filtering interleaved data.

Select register loading is discussed

in the LF Interface

TM

section.

ADDR

1

COEF

0

COEF

7

ADDR

2

COEF

0

COEF

7

ADDR

3

COEF

0

COEF

7

COEFFICIENT SET 1

COEFFICIENT SET 2

COEFFICIENT SET 3

CLK

LD

CF

11-0

W1

W1: Coefficient Set 1 written to coefficient banks during this clock cycle.

W2: Coefficient Set 2 written to coefficient banks during this clock cycle.

W3: Coefficient Set 3 written to coefficient banks during this clock cycle.

W2

W3

F

IGURE

6. C

OEFFICIENT

B

ANK

L

OADING

S

EQUENCE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LF3338QC12 | 8-Bit Vertical Digital Image Filter |

| LF3347 | High-Speed Image Filter with Coefficient RAM(高速圖像濾波器(帶系數(shù)RAM)) |

| LF3347QC12 | CAP 1.0UF 63V METAL POLY |

| LF3347QC15 | High-Speed Image Filter with Coefficient RAM |

| LF3370QC12 | High-Definition Video Format Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LF3338QC12 | 制造商:LOGIC 制造商全稱:LOGIC 功能描述:8-Bit Vertical Digital Image Filter |

| LF3347 | 制造商:LOGIC 制造商全稱:LOGIC 功能描述:High-Speed Image Filter with Coefficient RAM |

| LF3347D | 制造商:n/a 功能描述:3347 NSC'85 S8J2B |

| LF3347GC12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Filter |

| LF3347GC15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。