- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358760 > LC723740 (Sanyo Electric Co.,Ltd.) ETR Microcontrollers(大容量電子調(diào)諧應(yīng)用的微控制器) PDF資料下載

參數(shù)資料

| 型號: | LC723740 |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | ETR Microcontrollers(大容量電子調(diào)諧應(yīng)用的微控制器) |

| 中文描述: | 東突微控制器(大容量電子調(diào)諧應(yīng)用的微控制器) |

| 文件頁數(shù): | 14/14頁 |

| 文件大小: | 229K |

| 代理商: | LC723740 |

PS No. 5931-14/14

LC723732/40/48/56/64

This catalog provides information as of June, 1998. Specifications and information herein are subject to change

without notice.

I

No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace

equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of

which may directly or indirectly cause injury, death or property loss.

I

Anyone purchasing any products described or contained herein for an above-mentioned use shall:

Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and

distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all

damages, cost and expenses associated with such use:

Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on

SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees

jointly or severally.

I

Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for

volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied

regarding its use or any infringements of intellectual property rights or other rights of third parties.

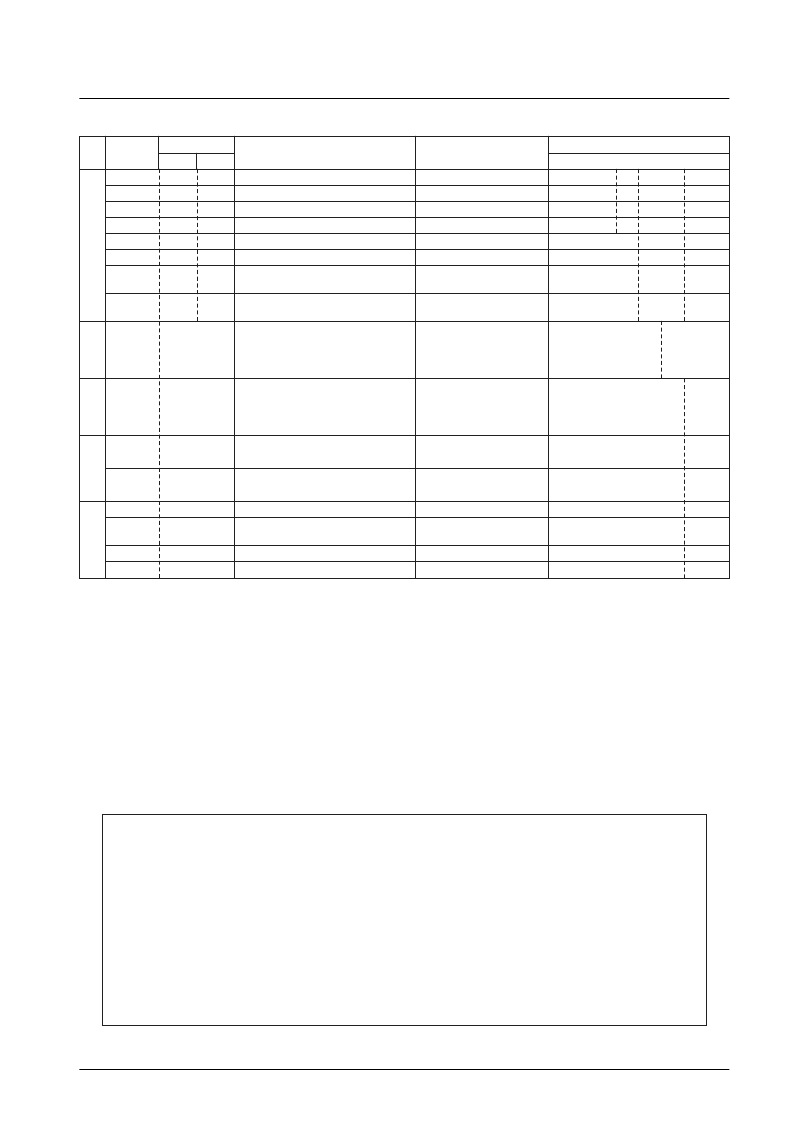

Continued from preceding page.

Mnemonic

Operand

Function

Operations function

Instruction format

1st

2nd

IN

M

P1n

Input port1 data to M

M

←

(P1n)

P1n

←

M

M

←

(P2n)

P2n

←

(M)

(P1n)N

←

1

(P1n)N

←

0

1 1 1 0 1 0 DH

DL

P1n

OUT

M

P1n

Output contents of M to port 1

1 1 1 0 1 1 DH

DL

P1n

INR

M

P2n

Input port 2 data to M

0 0 1 1 1 0 DH

DL

P2n

OUTR

M

P2n

Output contents of M to port 2

0 0 1 1 1 1 DH

DL

P2n

SPB

P1n

N

Set port 1 bits

0 0 0 0 0 0 1 0

P1n

N

RPB

P1n

N

Reset port 1 bits

0 0 0 0 0 0 1 1

P1n

N

TPT

P1n

N

Test port 1 bits, then skip if all bits

specified are true

if (P1n)N = all 1, then skip

1 1 1 1 1 1 0 0

P1n

N

TPF

P1n

N

Test port 1 bits, then skip if all bits

specified are false

if (P1n)N = all 0, then skip

1 1 1 1 1 1 0 1

P1n

N

BANK

I

Select Bank

BANK

←

I

1 1 1 1 1 0 0 1 0 0

I

MVTL

Move program memory data specified by

ADR to DTR

DTR

←

(ROM

ADR

)

0 0 0 0 0 0 0 0 0 0 1 1

PUSH

SR

Move ADR/DTR to stack

Stack

←

(ADR/DTR)

1 1 1 1 1 0 0 1 1 0 0 0

SR

POP

SR

Move stack to ADR/DTR

ADR/DTR

←

Stack

1 1 1 1 1 0 0 1 1 0 0 1

SR

PAGE

I

Set page flag

PAGE flag

←

I

HALT reg

←

I,

then CPU clock stop

0 0 0 0 0 0 0 0 0 1 1 1

I

HALT

I

Halt mode control

0 0 0 0 0 0 0 0 0 1 0 0

I

CKSTP

Clock stop

Stop xtal OSC if HOLD = 0

0 0 0 0 0 0 0 0 0 1 0 1

NOP

No operation

No operation

0 0 0 0 0 0 0 0 0 0 0 0

I

B

i

T

i

S

i

O

I

g

f e d c b a 9 8 7 6 5 4 3 2 1 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC723781N | CMOS IC Electronic tuning system for car audio ETR Microcontrollers |

| LC7265 | Received Frequency Display for Radio Receivers(用于無線電接收器接收頻率的顯示) |

| LC7267 | Digital Display of Clock/Receiving Frequency for Radio Set Applications(用于收音機時鐘/接收頻率數(shù)字顯示) |

| LC72700E | Mobile FM Multiplex Broadcast Receiver LSI(移動FM多路廣播接收器) |

| LC72705E | FM Multiplex Receiver IC for VICS Systems(用于VICS系統(tǒng)的FM多路接收器芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC723748 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:ETR Microcontrollers |

| LC723756 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:ETR Microcontrollers |

| LC723764 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:ETR Microcontrollers |

| LC723781N | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:CMOS IC Electronic tuning system for car audio ETR Microcontrollers |

| LC723782N | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:CMOS IC Electronic tuning system for car audio ETR Microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。