- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄39190 > LC07410LP SPECIALTY CONSUMER CIRCUIT, QCC40 PDF資料下載

參數(shù)資料

| 型號(hào): | LC07410LP |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, QCC40 |

| 封裝: | 5 X 5 MM, VQLP-40 |

| 文件頁(yè)數(shù): | 4/35頁(yè) |

| 文件大?。?/td> | 430K |

| 代理商: | LC07410LP |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

LC07410LP

No.A1207-12/35

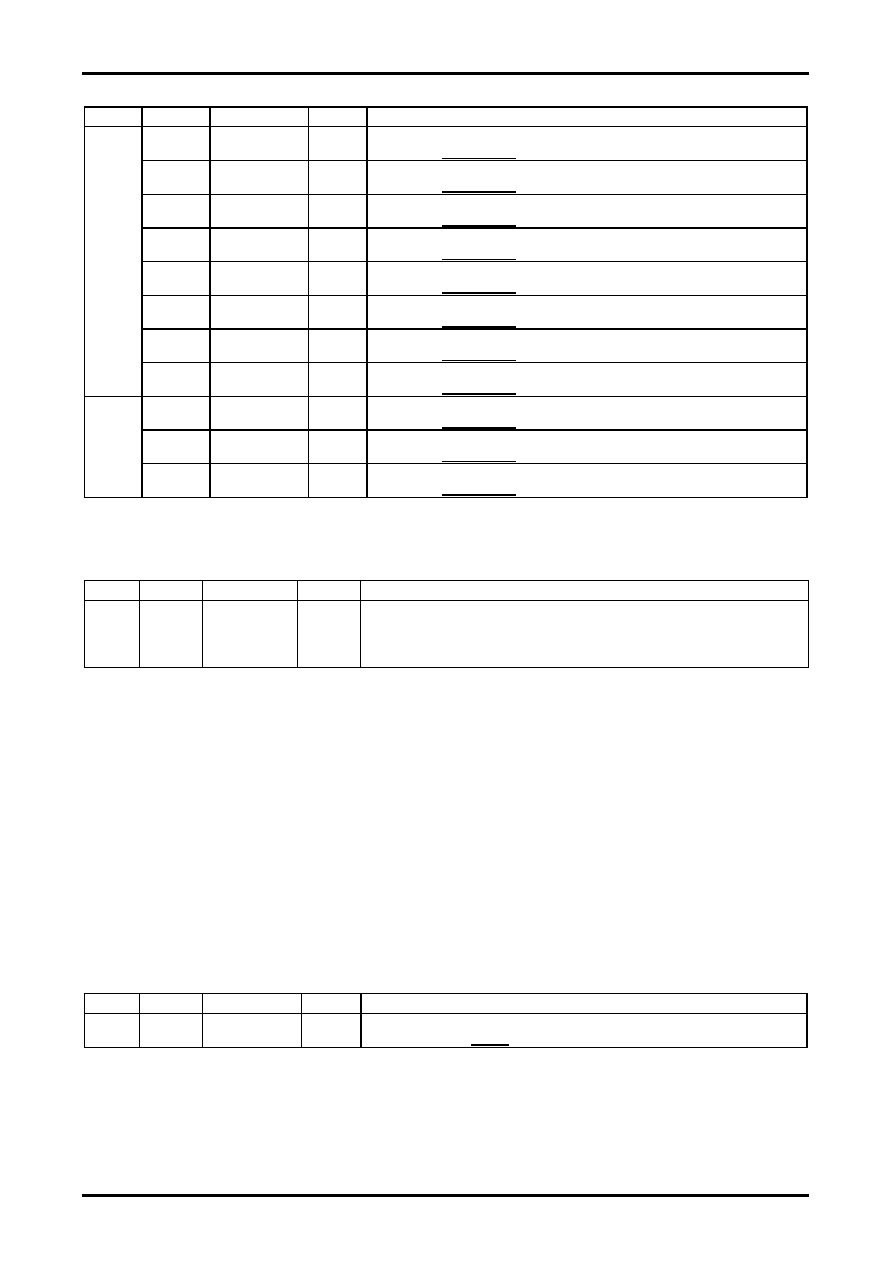

Power Control

ADRS

Bit

Name

Init

Description

[7]

MIC_PDX

0b

MIC amplifier circuit, power control

1: power on

0: power down

[6]

MIC_PWR_PDX

0b

MIC power circuit (MIC_PWR pin), power control

1: power on

0: power down

[5]

PGA_PDX

0b

PGA circuit, power control

1: power on

0: power down

[4]

ADC_PDX

0b

ADC circuit, power control

1: power on

0: power down

[3]

DAC_PDX

0b

DAC circuit, power control

1: power on

0: power down

[2]

SEL_PDX

0b

Selector (LOUT2) circuit, power control

1: power on

0: power down

[1]

LO_PDX

0b

Line out circuit (LOUT1) circuit, power control

1: power on

0: power down

00h

[0]

SP_PDX

0b

Speaker amplifier circuit, power control

1: power on

0: power down

[2]

PLL_PDX

0b

PLL circuit, power control

1: power on

0: power down (PLL-EXT mode)

[1]

REG_PDX

0b

Regulator circuit, power control

1: power on

0: power down

01h

[0]

VD_PDX

0b

Video driver circuit, power control

1: power on

0: power down

Sampling Frequency Setting

Set sampling frequency used by FS [4 : 0] register. This is necessary to make it for correctly setting digital frequency

characteristic and ALC damping time constant. The setting is adjusted to a value that is the closest to fs used.

ADRS

Bit

Name

Init

Description

15h

[3:0]

FS

1000b

Sampling Frequency Setting

1000: 48kHz/0111: 44.1kHz/0110: 32kHz/0101: 24kHz

0100: 22.05kHz/0011: 16kHz/0010: 12kHz/0001: 11.025kHz

0000: 8kHz

Note: This setting doesn’t synchronize with PLL setting. It is necessary to set it individually respectively.

Refer to the page of PLL function explanation for PLL setting.

3V Regulator

Built-in 3V Regulator for VDDA,VDDP.

The regulator starts by setting as REG_PDX=1.

Output current is 100mA (typ).

It provides with max 200mA (typ) output current limiter for overcurrent protective function.

Microphone (MIC) amplifier

The microphone amplifier has a differential input and a gain of +26dB (typ).

Its gain can also be set to +20dB or 0dB by register MGAIN [1:0]. Its input resistance is 70k

Ω (typ). The MICPWR is

a power output pin for the microphone, and its output voltage is 2.3V (typ 0.767*VDDA).

The maximum output current is 20mA.

The microphone amplifier is placed in the power down mode by setting MIC_PDX to 0.

When MIC_PWR_PDX is set to 0, the microphone power supply circuit is placed in the power down mode.

ADRS

Bit

Name

Init

Description

02h

[5:4]

MIC_GAIN

01b

MIC amplifier circuit, gain setting

11: 26dB 10: 20dB 01: 0dB 00: 0dB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC10.7-70000/07 | 10.7 MHz, BAND PASS FILTER |

| LC113.0-10.0/06 | 113 MHz, BAND PASS FILTER |

| LC120.0-2.0/03 | 120 MHz, BAND PASS FILTER |

| LC120.0-3.0/03 | 120 MHz, BAND PASS FILTER |

| LC1206L473MB | 1 FUNCTIONS, 25 V, 0.1 A, DATA LINE FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC074146LP | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:CMOS IC Monaural CODEC+Audio I/F +Video driver IC |

| LC07422T | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:CMOS IC Audio CODEC with Video Driver |

| LC07424LP | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:CMOS IC Audio CODEC with Video Driver |

| LC07424LP-MPB-E | 功能描述:接口—CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| LC08000E-2H | 制造商:ON Semiconductor 功能描述:MOTOR VECTOR CONTROL IC - Trays 制造商:ON Semiconductor 功能描述:FTRAY / MOTOR VECTOR CONTROL IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。