- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224103 > K4T56163QI-ZLD50 16M X 16 SYNCHRONOUS DRAM, 0.5 ns, PBGA84 PDF資料下載

參數(shù)資料

| 型號: | K4T56163QI-ZLD50 |

| 元件分類: | DRAM |

| 英文描述: | 16M X 16 SYNCHRONOUS DRAM, 0.5 ns, PBGA84 |

| 封裝: | ROHS COMPLIANT, FBGA-84 |

| 文件頁數(shù): | 26/42頁 |

| 文件大?。?/td> | 727K |

| 代理商: | K4T56163QI-ZLD50 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

Rev. 1.0 October 2007

DDR2 SDRAM

K4T56163QI

32 of 42

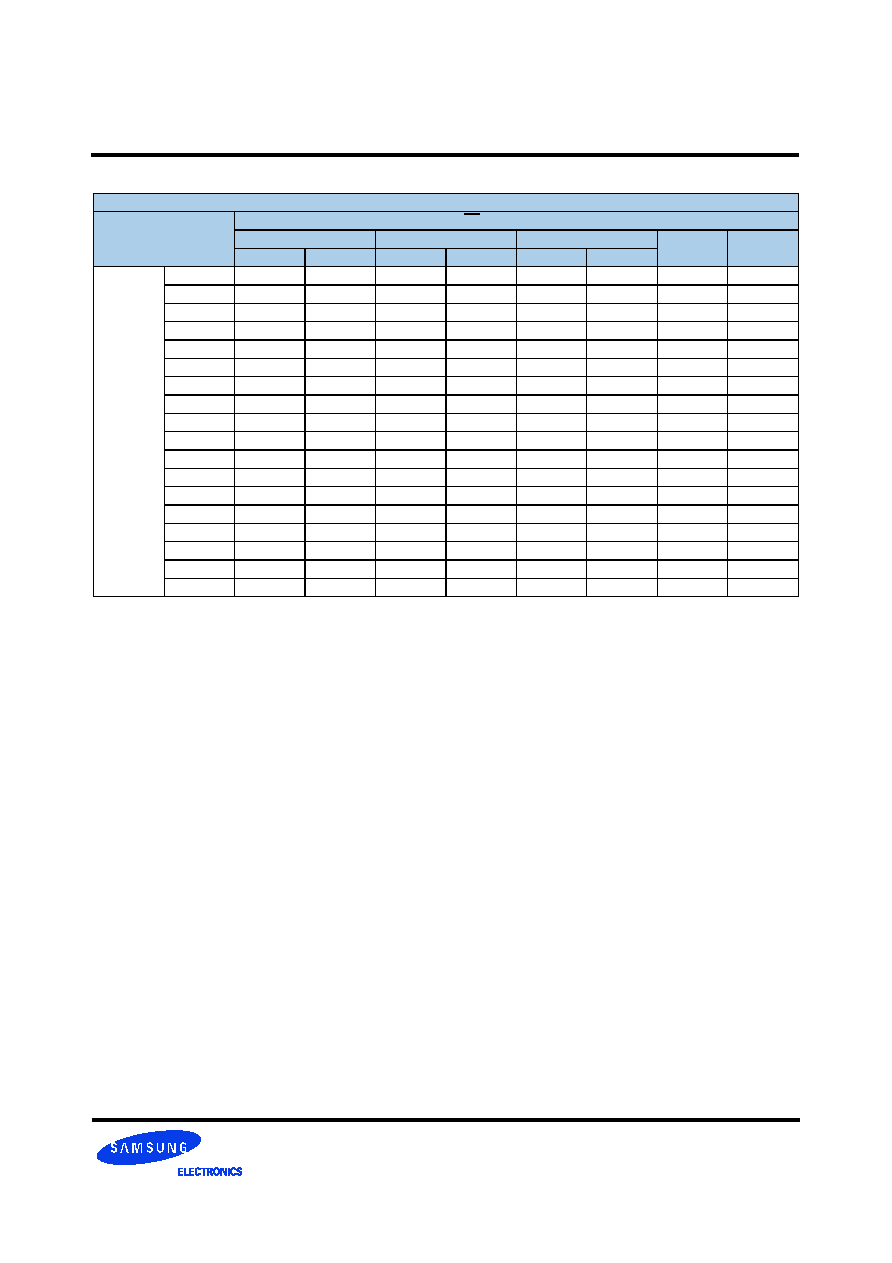

Table 5 - Derating values for DDR2-667, DDR2-800

For all input signals the total tIS (setup time) and tIH (hold time) required is calculated by adding the data sheet tIS(base) and tIH(base) value to the

tIS

and

tIH derating value respectively. Example: tIS (total setup time) = tIS(base) + tIS

Setup (tIS) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of VREF(dc) and the first crossing of Vih(ac)min.

Setup (tIS) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of VREF(dc) and the first crossing of Vil(ac)max. If

the actual signal is always earlier than the nominal slew rate line between shaded ’VREF(dc) to ac region’, use nominal slew rate for derating value (see

Figure 13). If the actual signal is later than the nominal slew rate line anywhere between shaded ’VREF(dc) to ac region’, the slew rate of a tangent line to

the actual signal from the ac level to dc level is used for derating value (see Figure 14).

Hold (tIH) nominal slew rate for a rising signal is defined as the slew rate between the last crossing of Vil(dc)max and the first crossing of VREF(dc). Hold

(tIH) nominal slew rate for a falling signal is defined as the slew rate between the last crossing of Vih(dc)min and the first crossing of VREF(dc). If the

actual signal is always later than the nominal slewrate line between shaded ’dc to VREF(dc) region’, use nominal slew rate for derating value (see Figure

15). If the actual signal is earlier than the nominal slew rate line anywhere between shaded ’dc to VREF(dc) region’, the slew rate of a tangent line to the

actual signal from the dc level to VREF(dc) level is used for derating value (see Figure 16).

Although for slow slew rates the total setup time might be negative (i.e. a valid input signal will not have reached VIH/IL(ac) at the time of the rising clock

transition) a valid input signal is still required to complete the transition and reach VIH/IL(ac).

For slew rates in between the values listed in Tables 4 and 5, the derating values may obtained by linear interpolation.

These values are typically not subject to production test. They are verified by design and characterization.

tIS and tIH Derating Values for DDR2-667, DDR2-800

CK, CK Differential Slew Rate

2.0 V/ns

1.5 V/ns

1.0 V/ns

Units

Notes

tIS

tIH

tIS

tIH

tIS

tIH

Command/

Address Slew

rate(V/ns)

4.0

+150

+94

+180

+124

+210

+154

ps

1

3.5

+143

+89

+173

+119

+203

+149

ps

1

3.0

+133

+83

+163

+113

+193

+143

ps

1

2.5

+120

+75

+150

+105

+180

+135

ps

1

2.0

+100

+45

+130

+75

+160

+105

ps

1

1.5

+67

+21

+97

+51

+127

+81

ps

1

1.0

0

+30

+60

ps

1

0.9

-5

-14

+25

+16

+55

+46

ps

1

0.8

-13

-31

+17

-1

+47

+29

ps

1

0.7

-22

-54+8-24

+38

+6

ps

1

0.6

-34

-83

-4

-53

+26

-23

ps

1

0.5

-60

-125

-30

-95

0

-65

ps

1

0.4

-100

-188

-70

-158

-40

-128

ps

1

0.3

-168

-292

-138

-262

-108

-232

ps

1

0.25

-200

-375

-170

-345

-140

-315

ps

1

0.2

-325

-500

-295

-470

-265

-440

ps

1

0.15

-517

-708

-487

-678

-457

-648

ps

1

0.1

-1000

-1125

-970

-1095

-940

-1065

ps

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K5A3240YT | Multi-Chip Package MEMORY 32M Bit (4Mx8/2Mx16) Dual Bank NOR Flash Memory / 4M(512Kx8/256Kx16) Full CMOS SRAM |

| K6R1004C1C | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

| K6R1004C1C-I | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

| K6R1004C1C-I10 | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

| K6R1004C1C-I12 | 256Kx4 Bit (with OE) High-Speed CMOS Static RAM(5.0V Operating). |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4T56163QN | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:Consumer Memory |

| K4T56163QN-HCE6000 | 制造商:Samsung SDI 功能描述:DRAM Chip DDR2 SDRAM 256M-Bit 16Mx16 1.8V 84-Pin FBGA Tray |

| K4T56163QN-HCE6T00 | 制造商:Samsung SDI 功能描述: |

| K4T56163QN-ZCE6T00 | 制造商:Samsung 功能描述:256 SDRAM X16 - Tape and Reel |

| K4T56163QN-ZCE7000 | 制造商:Samsung 功能描述:DDR2 SDRAM 32MX16 47H32M16 PBF FBGA 1.8V PLASTIC 512M - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。