- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299244 > K4H510838F-LCCC 64M X 8 DDR DRAM, 0.65 ns, PDSO66 PDF資料下載

參數(shù)資料

| 型號: | K4H510838F-LCCC |

| 元件分類: | DRAM |

| 英文描述: | 64M X 8 DDR DRAM, 0.65 ns, PDSO66 |

| 封裝: | 0.400 X 0.875 INCH, 0.65 MM PITCH, HALOGEN FREE AND ROHS COMPLIANT, TSOP2-66 |

| 文件頁數(shù): | 22/24頁 |

| 文件大?。?/td> | 361K |

| 代理商: | K4H510838F-LCCC |

Rev. 1.1 November 2008

DDR SDRAM

K4H510438F

K4H510838F

K4H511638F

7 of 24

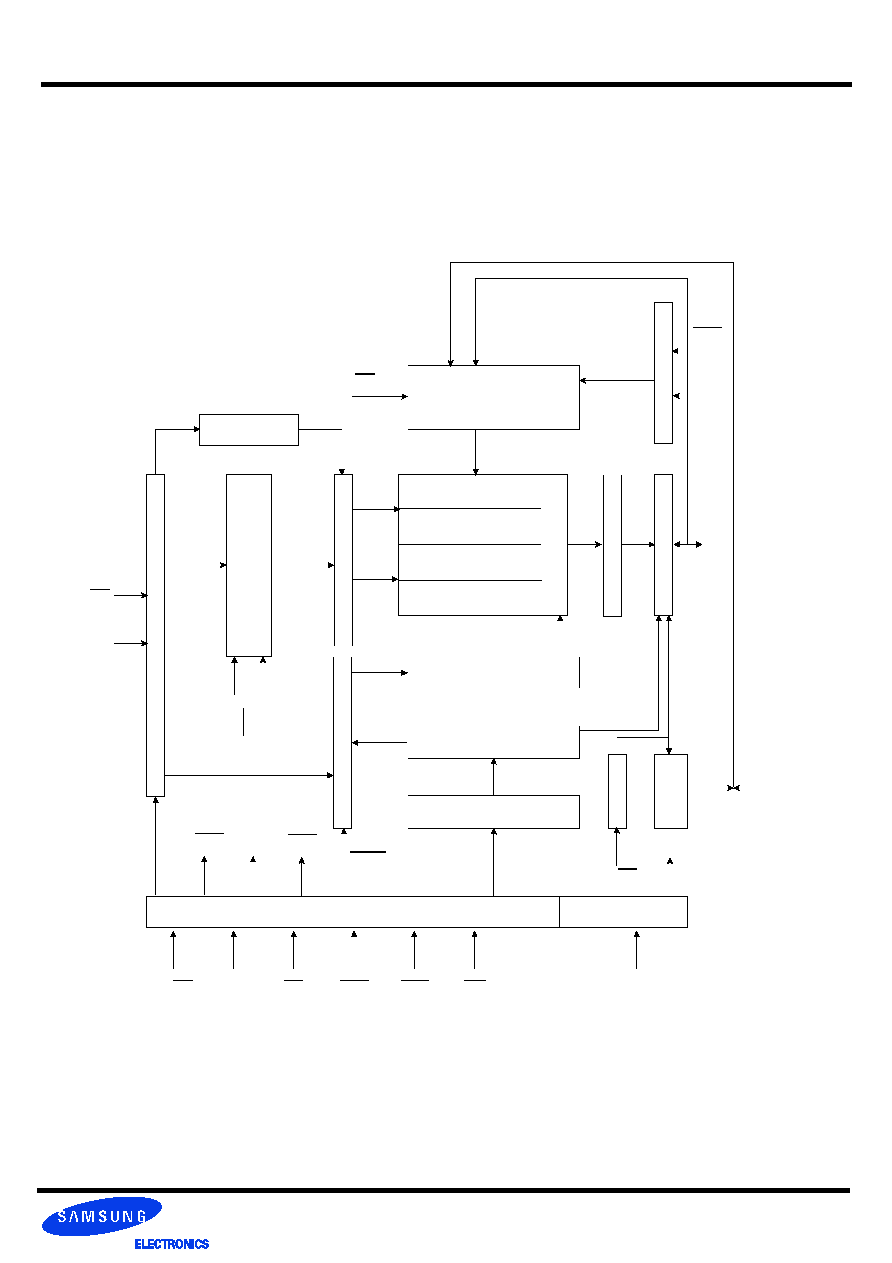

6.0 Block Diagram (32M x 4 / 16Mb x 8 / 8Mb x 16 I/O x4 Banks)

Bank Select

Timing Register

Address

Register

Re

fre

sh

C

ounter

Ro

w

Bu

ffe

r

Ro

w

Decode

r

Co

l.Buf

fer

Data Input Register

Serial to parallel

16Mx8/ 8Mx16/ 4Mx32

Se

ns

eAMP

2

-bit

p

refetch

O

utput

Buf

fer

I/O

Control

Column Decoder

Latency & Burst Length

Programming Register

DL

L

St

ro

b

e

Gen.

CK, CK

ADD

LCKE

CK, CK

CKE

CS

RAS

CAS

WE

CK, CK

LCAS

LRAS LCBR

LWE

LWCBR

LR

AS

LCBR

CK, CK

x8/x16/32

x4/x8/16

LWE

LDM (x4/x8)

x4/x8/16

DQi

Data Strobe

LUDM (x16)

LDM (x4/x8)

LUDM (x16)

DM Input Register

LDM (x4/x8)

LUDM (x16)

16Mx8/ 8Mx16/ 4Mx32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4S280432M-TC80 | 32M X 4 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| K4S280832M-TC1L0 | 16M X 8 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

| K4S281632D-TI7C | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| K4S281632D-TP7C | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| K50-3C0E35.3280MR | CRYSTAL OSCILLATOR, CLOCK, 35.328 MHz, CMOS OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4H510838G | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:Consumer Memory |

| K4H510838G-LC/LB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb G-die DDR SDRAM Specification |

| K4H510838G-LC/LCC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Mb G-die DDR SDRAM Specification |

| K4H510838J-BCB3000 | 制造商:Samsung Semiconductor 功能描述:K4H510838J-BCB3000 - Trays |

| K4H510838J-BCCC000 | 制造商:Samsung Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。