- 您現(xiàn)在的位置:買賣IC網 > Datasheet目錄40 > IPM6220ACAZ-T (Intersil)IC REG 5OUT BUCK/LDO SYNC 24SSOP Datasheet資料下載

參數(shù)資料

| 型號: | IPM6220ACAZ-T |

| 廠商: | Intersil |

| 文件頁數(shù): | 13/15頁 |

| 文件大?。?/td> | 527K |

| 描述: | IC REG 5OUT BUCK/LDO SYNC 24SSOP |

| 標準包裝: | 2,500 |

| 拓撲: | 降壓(降壓)同步(3),線性(LDO)(2) |

| 功能: | 任何功能 |

| 輸出數(shù): | 5 |

| 頻率 - 開關: | 300kHz |

| 電壓/電流 - 輸出 1: | 控制器 |

| 電壓/電流 - 輸出 2: | 控制器 |

| 電壓/電流 - 輸出 3: | 控制器 |

| 帶 LED 驅動器: | 無 |

| 帶監(jiān)控器: | 無 |

| 帶序列發(fā)生器: | 是 |

| 電源電壓: | 5.6 V ~ 24 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | * |

| 封裝/外殼: | * |

| 供應商設備封裝: | * |

| 包裝: | * |

13

magnitude of voltage spikes. See the Application Note

AN9915 for the evaluation board component placement and

the printed circuit board layout details.

There are two sets of critical components in a DC-DC

converter using an IPM6220A controller. The switching

power components are the most critical because they switch

large amounts of energy, and as such, they tend to generate

equally large amounts of noise. The critical small signal

components are those connected to sensitive nodes or

those supplying critical bias currents.

Power Components Layout Considerations

The power components and the controller IC should be

placed first. Locate the input capacitors, especially the high-

frequency ceramic decoupling capacitors, close to the power

MOSFETs. Locate the output inductor and output capacitors

between the MOSFETs and the load. Locate the PWM

controller close to the MOSFETs.

Insure the current paths from the input capacitors to the

MOSFETs, to the output inductors and output capacitors are

as short as possible with maximum allowable trace widths.

A multi-layer printed circuit board is recommended. Dedicate

one solid layer for a ground plane and make all critical

component ground connections with vias to this layer.

Dedicate another solid layer as a power plane and break this

plane into smaller islands of common voltage levels. The

power plane should support the input power and output power

nodes. Use copper filled polygons on the top and bottom

circuit layers for the phase nodes, but do not unnecessarily

oversize these particular islands. Since the phase nodes are

subjected to very high dV/dt voltages, the stray capacitor

formed between these islands and the surrounding circuitry

will tend to couple switching noise. Use the remaining printed

circuit layers for small signal wiring. The wiring traces from the

control IC to the MOSFET gate and source should be sized to

carry 2A peak currents.

Small Components Signal Layout Considerations

4. The VSNS1 and VSNS2 inputs should be bypassed with

a 1.0礔 capacitor close to their respective IC pins.

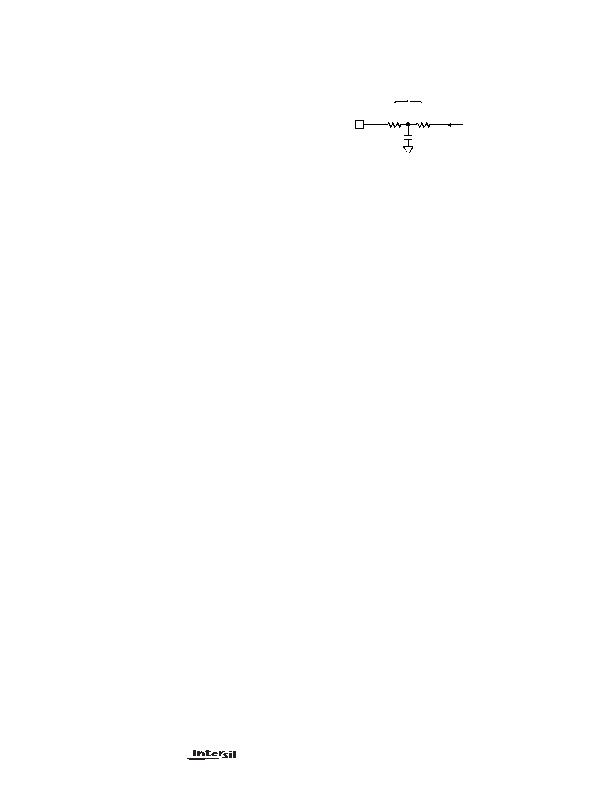

5. A T filter consisting of a split RSNS and a small, 100pF,

capacitor as shown in Figure 10, may be helpful in

reducing noise coupling into the ISEN input. For example,

if the calculated value of RSNS1 is 2.2k&, dividing it as

shown with a 100pF capacitor provides filtering without

changing the current limit set point. For any calculated

value of RSNS, keep the value of the R9 portion to

approximately 200&, and the remainder of the resistance

in the R19 position. The 200& resistor and 100pF

capacitor provide effective filtering for noise above 8MHz.

This filter configuration may be helpful on both the 3.3V and

5V Main outputs.

6. The bypass capacitors for VBATT and the soft-start

capacitors, C

SS1

and C

SS2

should be located close to

their connecting pins on the control IC. Minimize any

leakage current paths from SDWN1 and SDWN2 nodes,

since the internal current source is only 5礎.

7. Refer to the Application Note AN9915 for a

recommended component placement and

interconnections.

Figure 11 shows an application circuit of a power supply for a

notebook PC microprocessor system. The power supply

provides +5V ALWAYS, +3.3V ALWAYS, +5.0V, +3.3V, and

12V from +5.6-22V

DC

battery voltage. For detailed information

on the circuit, including a Bill of Materials and circuit board

description, see Application Note AN9915. Also see Intersils

web site (www.intersil.com) for the latest information.

ISEN1

R19

R9

200

2K

C12

100pF

FROM PHASE

NODE

RSNS = R19 + R9

FIGURE 10. NOISE FILTER FOR ISEN1 INPUT

IPM6220A

相關PDF資料 |

PDF描述 |

|---|---|

| IR2170 | IC CURRENT SENSE 600V 1MA 8-DIP |

| IR2171STR | IC CURRENT SENSE 8SOIC |

| IR2172S | IC CURRENT SENSE 8SOIC |

| IR2175STR | IC CURRENT SENSE 0.5% 8SOIC |

| IR22771STRPBF | IC CURRENT SENSE 16SOIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IPM6220CA | 制造商:Rochester Electronics LLC 功能描述:MULTI-OUTPUT SYSTEM ELECTRONICS REGULATOR FOR MOBIL PCS - Bulk |

| IPM6220CB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| IPM6220EVAL1 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:Advanced Triple PWM Only Mode and Dual Linear Power Controller for Portable Applications |

| IPM-C112 | 制造商:JDSU 制造商全稱:JDS Uniphase Corporation 功能描述:Miniature Integrated Power Monitor |

| IPM-C113 | 制造商:JDSU 制造商全稱:JDS Uniphase Corporation 功能描述:Miniature Integrated Power Monitor |

發(fā)布緊急采購,3分鐘左右您將得到回復。