- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67712 > IDT72T6360L7-5BBI (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PBGA324 PDF資料下載

參數(shù)資料

| 型號: | IDT72T6360L7-5BBI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA324 |

| 封裝: | 19 X 19 MM, 1 MM PITCH, PLASTIC, BGA-324 |

| 文件頁數(shù): | 40/51頁 |

| 文件大?。?/td> | 508K |

| 代理商: | IDT72T6360L7-5BBI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

45

IDT72T6360 2.5V, SEQUENTIAL FLOW-CONTROL DEVICE

x9, x18, x36 BIT WIDE CONFIGURATION

COMMERCIALANDINDUSTRIAL

TEMPERATURERANGES

OCTOBER 10, 2005

JTAG TIMING SPECIFICATIONS

(IEEE 1149.1 COMPLIANT)

The JTAG test port in this device is fully compliant with the IEEE Standard

TestAccessPort(IEEE1149.1)specifications.Fouradditionalpins(TDI,TDO,

TMS and TCK) are provided to support the JTAG boundary scan interface.

Note that IDT provides appropriate Boundary Scan Description Language

program files for these devices.

The Standard JTAG interface consists of seven basic elements:

Test Access Port (TAP)

TAP controller

Instruction Register (IR)

Data Register Port (DR)

Bypass Register (BYR)

ID Code Register

The following sections provide a brief description of each element. For a

completedescriptionrefertotheIEEEStandardTestAccessPortSpecification

(IEEE Std. 1149.1-1990).

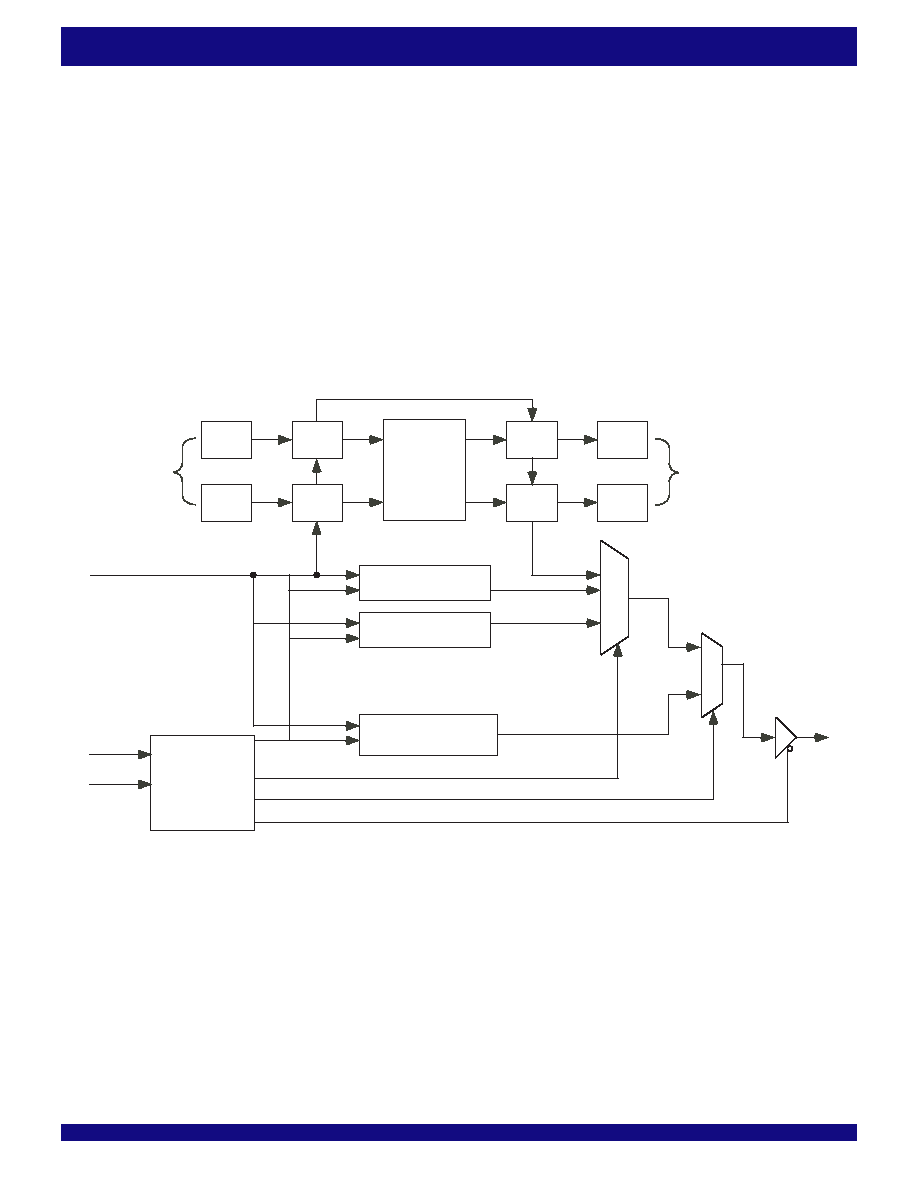

The Figure below shows the standard Boundary-Scan Architecture

Figure 32. JTAG Architecture

TEST ACCESS PORT (TAP)

The TAP interface is a general-purpose port that provides access to the

internal JTAG state machine. It consists of three input ports (TCLK, TMS, TDI)

and one output port (TDO).

THE TAP CONTROLLER

The TAP controller is a synchronous finite state machine that responds to

TMS and TCLK signals to generate clock and control signals to the Instruction

and Data Registers for capture and updating of data passed through the TDI

serial input.

In Pad

Incell

Core

Logic

Outcell

Out Pad

All outputs

All inputs

Eg: Dins, Clks

(BSDL file

describes the

chain order)

ID

Bypass

Instruction

Register

TAP

TMS

TDI

TCK

Instruction

Select

Enable

TDO

6357 drw46

相關PDF資料 |

PDF描述 |

|---|---|

| IDT72T6360L6BBGI | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA324 |

| IDT73210ATC | 73 SERIES, 9-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, CDIP24 |

| IDT73211ATCB | 73 SERIES, 9-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, CDIP24 |

| IDT73210TC | 73 SERIES, 9-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, CDIP24 |

| IDT73211TCB | 73 SERIES, 9-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, CDIP24 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72T6480L10BB | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L10BBI | 功能描述:IC FLOW-CTRL 48BIT 10NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L7-5BB | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T6480L7-5BBG | 功能描述:IC FLOW-CTRL 48BIT 7-5NS 324-BGA RoHS:是 類別:集成電路 (IC) >> 專用 IC 系列:- 產(chǎn)品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- 類型:調幀器 應用:數(shù)據(jù)傳輸 安裝類型:表面貼裝 封裝/外殼:400-BBGA 供應商設備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT72T72105L10BB | 功能描述:IC FIFO 65536X72 10NS 324-BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72T 標準包裝:15 系列:74F 功能:異步 存儲容量:256(64 x 4) 數(shù)據(jù)速率:- 訪問時間:- 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:24-DIP(0.300",7.62mm) 供應商設備封裝:24-PDIP 包裝:管件 其它名稱:74F433 |

發(fā)布緊急采購,3分鐘左右您將得到回復。