- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372107 > SA7016DH (NXP SEMICONDUCTORS) 1.3GHz low voltage fractional-N synthesizer PDF資料下載

參數(shù)資料

| 型號: | SA7016DH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | XO, clock |

| 英文描述: | 1.3GHz low voltage fractional-N synthesizer |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, 1300 MHz, PDSO16 |

| 封裝: | PLASTIC, TSSOP-16 |

| 文件頁數(shù): | 12/18頁 |

| 文件大?。?/td> | 232K |

| 代理商: | SA7016DH |

Philips Semiconductors

Product specification

SA7016

1.3GHz low voltage fractional-N synthesizer

1999 Nov 04

12

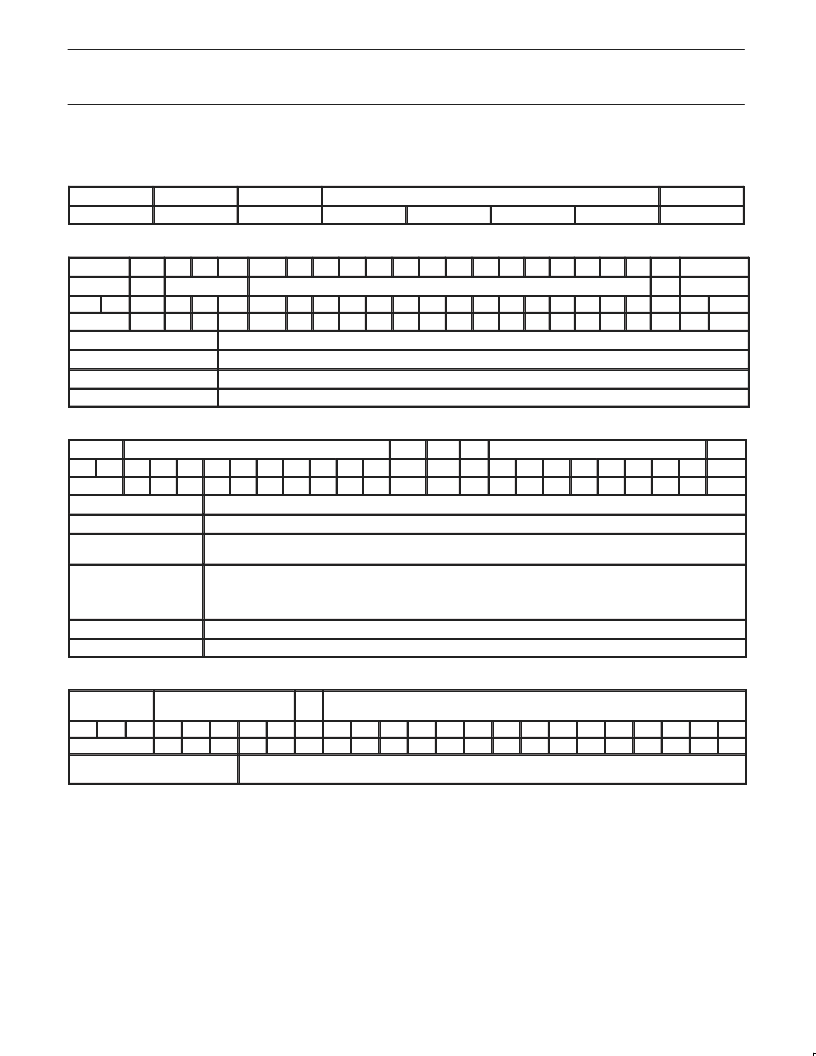

Data format

Table 1. Format of programmed data

LAST IN

MSB

SERIAL PROGRAMMING FORMAT

FIRST IN LSB

p23

p22

p21

p20

../..

../..

p1

p0

Table 2. A word, length 24 bits

LAST IN

MSB

LSB

FIRST IN

Address

fmod

Fractional-N

Main Divider ratio

Spare

0

0

FM

NF2

NF1

NF0

N15

N14

N13

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

N2

N1

N0

SP1

SP2

Default:

0

0

1

0

0

0

1

0

0

0

1

0

0

0

1

1

0

0

0

0

0

0

A word select

Fixed to 00.

Fractional Modulus select

FM 0 = modulo 8, 1 = modulo 5.

Fractional-N Increment

NF2..0 Fractional N Increment values 000 to 111.

N-Divider

N0..N15, Main divider values 512 to 65535 allowed for divider ratio.

Table 3. B word, length 24 bits

Address

REFERENCE DIVIDER

LOCK

PD

CP

FRACTIONAL COMPENSATION DAC

SPARE

0

1

R9

R8

R7

R6

R5

R4

R3

R2

R1

R0

LO

MAIN

CP0

FC7

FC6

FC5

FC4

FC3

FC2

FC1

FC0

SP3

Default:

0

0

0

1

0

1

0

0

0

1

0

0

0

0

1

0

1

0

0

0

0

0

B word select

Fixed to 01

R-Divider

R0..R9, Reference divider values 4 to 1023 allowed for divider ration.

Charge pump current

Ratio

CP0: Charge pump current ratio, see table of charge pump currents.

Lock detect output

L0

0

1

When main loop is in power down mode, the lock indicator is low.

Main lock detect signal present at the LOCK pin (push/pull).

Main lock detect signal present at the LOCK pin (open drain).

Power down

Main = 1: power to main divider, reference divider, main charge pumps, Main = 0 to power down.

Fractional Compensation

FC7..0 Fractional Compensation charge pump current DAC, values 0 to 255.

Table 4. D word, length 24 bits

Address

SYNTHESIZER TEST

BITS

SYNTHESIZER TEST BITS

1

1

0

–

–

–

–

–

Tspu

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

Default:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Tspu: Speed up = 1

Forces the main charge pumps in speed-up mode all the time.

NOTE

: All test bits must be set to 0 for normal operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SA701 | Divide by: 128/129-64/65 dual modulus low power ECL prescaler |

| SA701D | Divide by: 128/129-64/65 dual modulus low power ECL prescaler |

| SA701N | Divide by: 128/129-64/65 dual modulus low power ECL prescaler |

| SA701 | SILICON GATE ENHANCEMENT MODE RF POWER VDMOS TRANSISTOR |

| SA7025 | Low-voltage 1GHz fractional-N synthesizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SA701D | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Divide by: 128/129-64/65 dual modulus low power ECL prescaler |

| SA701N | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Divide by: 128/129-64/65 dual modulus low power ECL prescaler |

| SA702 | 制造商:POLYFET 制造商全稱:Polyfet RF Devices 功能描述:SILICON GATE ENHANCEMENT MODE RF POWER VDMOS TRANSISTOR |

| SA702/DF9M | 制造商:Hirose 功能描述:903-4508-0-00 EACH 制造商:Hirose 功能描述:SA702/DF9M |

| SA702/DF9M(62) | 制造商:Hirose 功能描述:903-4508-0-62 EACH 制造商:Hirose 功能描述:SA702/DF9M(62) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。