- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379205 > IBM13V51649AN (IBM Microeletronics) 512K x 64 SGRAM SO DIMM(Small Outline Dual In-line Memory Modules)(512K x 64 144腳小外形雙列直插同步圖形RAM模塊) PDF資料下載

參數(shù)資料

| 型號: | IBM13V51649AN |

| 廠商: | IBM Microeletronics |

| 英文描述: | 512K x 64 SGRAM SO DIMM(Small Outline Dual In-line Memory Modules)(512K x 64 144腳小外形雙列直插同步圖形RAM模塊) |

| 中文描述: | 為512k × 64 SGRAM蘇內(nèi)存(小外形雙列直插式內(nèi)存模塊)(為512k × 64 144腳小外形雙列直插同步圖形內(nèi)存模塊) |

| 文件頁數(shù): | 4/14頁 |

| 文件大?。?/td> | 224K |

| 代理商: | IBM13V51649AN |

IBM13V25649AN IBM13V51649AN

256K/512K x 64 SGRAM SO DIMM

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 4 of 14

88H4121.E24358

Revised 1/98

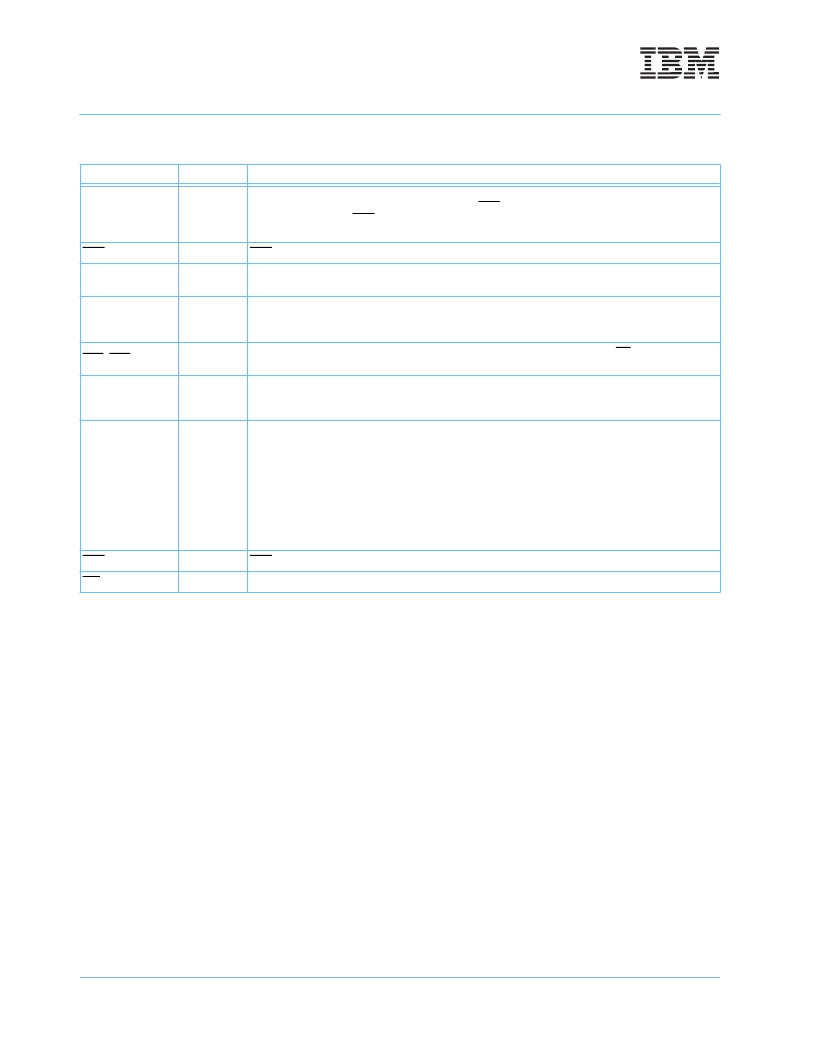

Signal Descriptions

Name

I/O

Function

A

0

-A

8

, (A

9

)

I

Address bits A

0

-A

8

are row addresses when Active command is activated.

Address bits A

0

-A

7

are column addresses when CAS is active.

Address bit A

8

, when CAS is active, enables/disables Auto Precharge.

Address bit A

9

selects which of the two memory banks is to be used.

CAS

I

CAS is part of the input command to the SGRAM.

CKE

I

Clock Enable disables the SGRAM clock internally, thus allowing data to remain on the output for

several CLK cycles. Clock Enable is also used as part of the input command to specify self-refresh.

CK0, CK1

I

CKn is driven by the system clock. All SGRAM input signals are sampled on the positive edge of

CKn. CKn also increments the internal burst counter and controls the output registers. CK1 is not

present on 256K x 64 SO DIMMS.

CS0, CS1

I

Chip Select indicates that the command on the input lines is for this device. If CSn are high, the

input command(s) will be ignored.

DQ

0

-DQ

63

I/O

Data Input/Output lines transfer data between the memory array and the system bus. These are

also input mask bits for Write-per-Bit. When Block Write is activated, DQs provide column address

mask.

DQMB

0

-DQMB

7

I

During Read, DQMB=1 turns off the output buffers.

During Write, DQMB=1 prevents a write to the current memory location.

DQMB

0

corresponds to the lowest byte (DQ

0

-DQ

7

).

DQMB

1

corresponds to DQ

8-15

.

DQMB

2

corresponds to DQ

16-23

.

DQMB

3

corresponds to DQ

24-31

.

DQMB

4

corresponds to DQ

32-39

.

DQMB

5

corresponds to DQ

40-47

.

DQMB

6

corresponds to DQ

48-55

.

DQMB

7

corresponds to DQ

56-63

.

RAS

I

RAS is part of the input command to the SGRAM.

WE

I

Write Enable is part of the input command.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM2520L8767 | IBM Asynchronous Transfer Mode Processor for ATM Resources(IBM異步轉(zhuǎn)換模式 ATM資源管理微處理器) |

| IBM25CPC710AB3A100 | IBM Dual Bridge and Memory Controller(IBM雙橋和存儲器控制器(連接帶同步動態(tài)RAM存儲器的Power PC 60x總線和兩個PCI端口)) |

| IBM3206K0424 | IBM Processor for Network Resources(異步轉(zhuǎn)換模式(ATM)32位微處理器(用于網(wǎng)絡(luò)資源管理)) |

| IBM3209K3114 | IBM Packet Routing Switch Serial Interface Converter(IBM封裝路線選擇開關(guān)串行接口轉(zhuǎn)換器) |

| IBM32NPCXX1EPABBE66 | IBM Processor for Network Resources(異步轉(zhuǎn)換模式(ATM)32位微處理器(用于網(wǎng)絡(luò)資源管理)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM14H5481 | 制造商:AVED Memory Products 功能描述: |

| IBM14H5540 | 制造商:AVED MEMORY PRODUCTS 功能描述: 制造商:AVED Memory Products 功能描述: |

| IBM17R8251 | 制造商:AVED Memory Products 功能描述: |

| IBM17R8252 | 制造商:AVED Memory Products 功能描述: |

| IBM1805T | 制造商:Schneider Electric 功能描述:IBM1805T |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。