- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370806 > HYS72D128520GR-8-B (INFINEON TECHNOLOGIES AG) Connector Wall Plate; Color:Almond; Leaded Process Compatible:Yes; No. of Ports:4 RoHS Compliant: Yes PDF資料下載

參數(shù)資料

| 型號(hào): | HYS72D128520GR-8-B |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | Connector Wall Plate; Color:Almond; Leaded Process Compatible:Yes; No. of Ports:4 RoHS Compliant: Yes |

| 中文描述: | 超薄注冊(cè)的DDR - SDRAM的我模塊 |

| 文件頁(yè)數(shù): | 9/22頁(yè) |

| 文件大小: | 409K |

| 代理商: | HYS72D128520GR-8-B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

HYS 72Dxx5xxGR-7F/7/8-B

Registered DDR-I SDRAM-Modules

INFINEON Technologies

9

2002-08-16 (0.91)

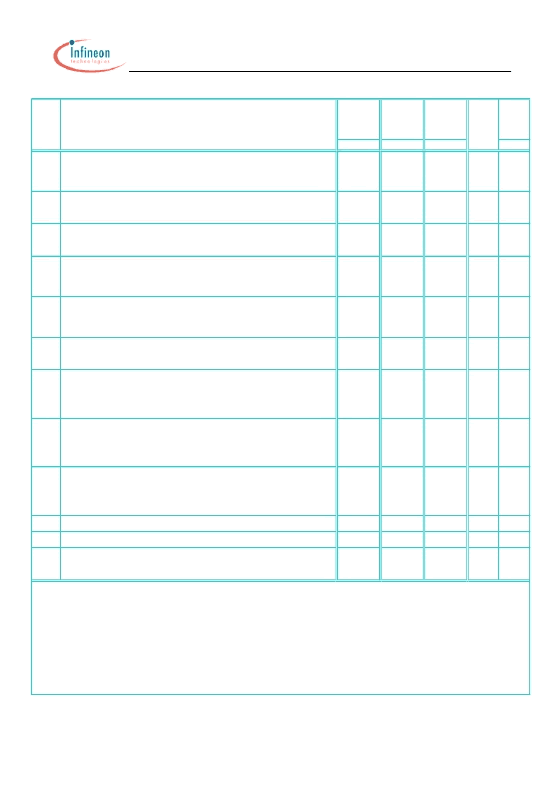

Operating, Standby and Refresh Currents (-8: PC1600)

Notes

5

IDD2P

mA

2, 4

IDD2F

mA

2, 4

IDD2Q

mA

2, 4

IDD3P

mA

2, 4

IDD5

mA

1, 4

1. The module IDD values are calculated from the component IDD datasheet values as:

n * IDDx[component]

for single bank modules (n: number of components per module bank)

n * IDDx[component] + n * IDD3N[component]

2. The module IDD values are calculated from the component IDD datasheet values as:

n * IDDx[component]

for single bank modules (n: number of components per module bank)

2 * n * IDDx[component]

for two bank modules (n: number of components per module bank)

3. DQ I/O (IDDQ) currents are not included into calculations: module IDD values will be measured differently depending on load conditions

4. DRAM component currents only: module IDD will be measured differently depending upon register and PLL operation currents

5. Test condition for maximum values: VDD = 2.7V ,Ta = 10°C

for two bank modules (n: number of components per module bank)

90

4590

1620

2520

2700

3870

1890

3780

1890

1GB

x72

2bank

-8

MA

X

2430

2610

252

1260

792

576

1530

3060

22,5

45

405

810

855

1710

198

396

144

288

1800

63

126

315

630

256MB

x72

1bank

-8

MA

X

512MB

x72

1bank

-8

MA

X

IDD7

IDD6

Operating Current

: four bank

;

four bank interleaving with BL=4

;

Refer to the following page for detailed test conditions.

Self-Refresh Current

: CKE

<

= 0.2V

;

external clock on

;

tCK = tCK MIN

Auto-Refresh Current

: tRC = tRFC MIN, distributed refresh

945

1, 3, 4

mA

mA

Symbol

Unit

Parameter/Condition

IDD4W

IDD4R

IDD3N

IDD1

2, 4

1, 4

Precharge Quiet Standby Current

: /CS >= VIH MIN, all banks idle

;

CKE >= VIH MIN

;

tCK = tCK MIN ,address and other control inputs stable at >=

VIH MIN or

<

= VIL MA

X;

VIN = VREF for DQ, DQS and DM.

IDD0

Operating Current

: one bank

;

active/read/precharge

;

Burst = 4

;

Refer to the following page for detailed test conditions.

Operating Current

: one bank

;

active / precharge

;

tRC = tRC MIN

;

tCK = tCK

MIN

;

DQ, DM, and DQS inputs changing once per clock cycle

;

address and

control inputs changing once every two clock cycles

Precharge Power-Down Standby Current

: all banks idle

;

power-down mode

;

CKE

<

= VIL MA

X;

tCK = tCK MIN

Precharge Floating Standby Current

: /CS >= VIH MIN, all banks idle

;

CKE >=

VIH MIN

;

tCK = tCK MIN ,address and other control inputs changing once per

clock cycle, VIN = VREF for DQ, DQS and DM.

810

1620

900

Active Power-Down Standby Current

: one bank active

;

power-down mode

;

CKE

<

= VIL MA

X;

tCK = tCK MIN

;

VIN = VREF for DQ, DQS and DM.

Active Standby Current

: one bank active

;

active / precharge

;

CS >= VIH MIN

;

CKE >= VIH MIN

;

tRC = tRAS MA

X;

tCK = tCK MIN

;

DQ, DM, and DQS inputs

changing twice per clock cycle

;

address and control inputs changing once per

clock cycle

Operating Current

: one bank active

;

Burst = 2

;

reads

;

continuous burst

;

address

and control inputs changing once per clock cycle

;

50% of data outputs changing

on every clock edge

;

CL = 2 for DDR200, and DDR266A, CL=3 for DDR333

;

tCK

= tCK MIN

;

IOUT = 0mA

Operating Current

: one bank active

;

Burst = 2

;

writes

;

continuous burst

;

address

and control inputs changing once per clock cycle

;

50% of data outputs changing

on every clock edge

;

CL = 2 for DDR200, and DDR266A, CL=3 for DDR333

;

tCK

= tCK MIN

mA

1, 3, 4

2, 4

mA

mA

1, 4

mA

mA

1, 3, 4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYS72D64000GR-7-B | 2.5 V 184-pin Registered DDR-I SDRAM Modules |

| HYS72D128020GR-7-B | Modular Connector; No. of Contacts:8; Approval Categories:Fire-Retardant UL 94V-0 Rated; Body Material:Plastic; Color:Blue; Contact Material:Phosphor Bronze; Contact Termination:Punchdown RoHS Compliant: Yes |

| HYS72D128021GR-7-B | Connector Wall Plate; Color:White; Leaded Process Compatible:Yes; No. of Ports:4 RoHS Compliant: Yes |

| HYS72D128021GR-8-B | Connector Wall Plate; Color:Almond; Leaded Process Compatible:Yes; No. of Ports:6 RoHS Compliant: Yes |

| HYS72D64020GR-7-B | 2.5 V 184-pin Registered DDR-I SDRAM Modules |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72D128521GR-7-B | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:Low Profile Registered DDR-I SDRAM-Modules |

| HYS72D128521GR-7F-B | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:Low Profile Registered DDR-I SDRAM-Modules |

| HYS72D128521GR-8-B | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:Low Profile Registered DDR-I SDRAM-Modules |

| HYS72D128900HBR-6-C | 制造商:QIMONDA 制造商全稱(chēng):QIMONDA 功能描述:184-Pin Registered Double-Data-Rate SDRAM Module |

| HYS72D16000GR | 制造商:INFINEON 制造商全稱(chēng):Infineon Technologies AG 功能描述:Registered DDR SDRAM-Modules |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。