- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370783 > HYB25D128323C-3 (INFINEON TECHNOLOGIES AG) 128 Mbit DDR SGRAM PDF資料下載

參數(shù)資料

| 型號: | HYB25D128323C-3 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 128 Mbit DDR SGRAM |

| 中文描述: | 128兆的DDR SGRAM |

| 文件頁數(shù): | 16/53頁 |

| 文件大小: | 734K |

| 代理商: | HYB25D128323C-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

HYB25D128323C[-3/-3.3/-3.6/-4.5/-5.0/L3.6/L4.5]

128 Mbit DDR SGRAM [4M x 32]

Register Set

Data Sheet

16

V1.7, 2003-07

3.2

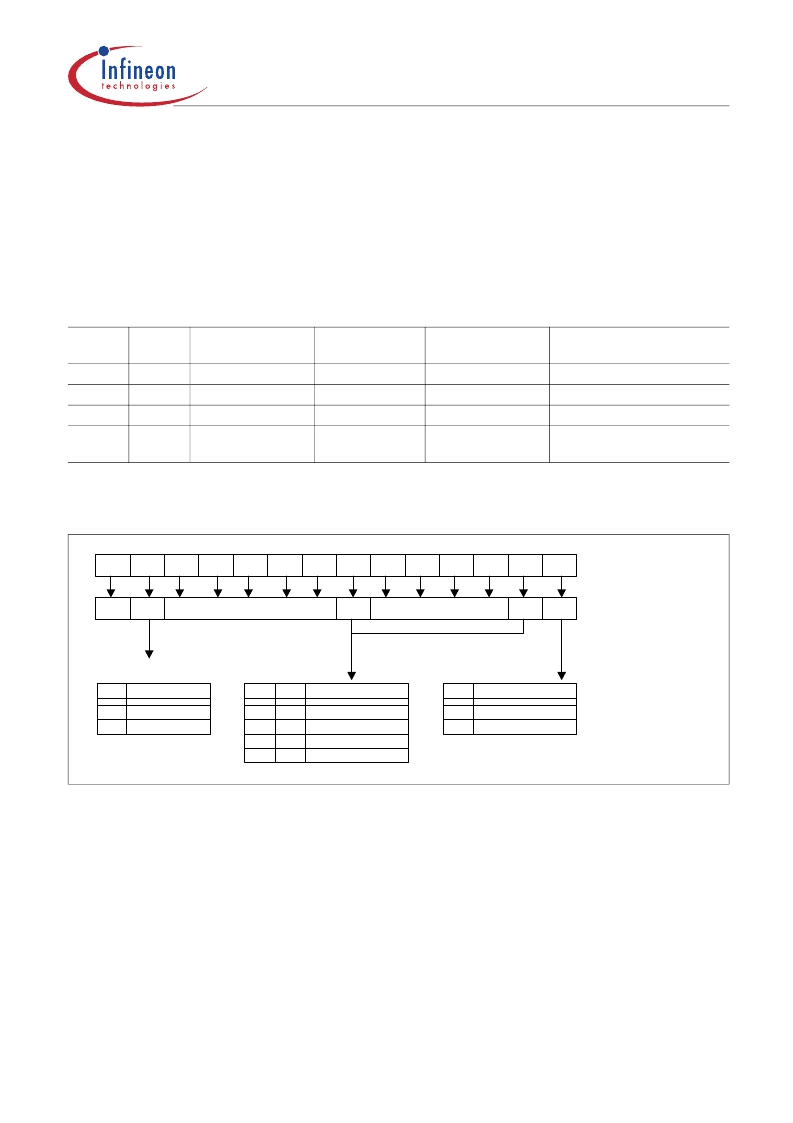

Extended Mode Register Setup (EMRS)

The Extended Mode Register is responsible for enabling / disabling the DLL in the HYB25D128323C and for

selecting the interface type for the IOs and input pins. The Extended Mode Register can be programmed by

performing a normal Mode Register Setup operation and setting the BA0 bit to high. All other bits of the EMRS

register are reserved and should be set to low.

The Bit A0 enables / disables the DLL.

The Bits A1 and A6 set the driver strength of the IOs. For detailed explanation, refer to the following table.

Note:The combination A6=0 and A1=0 defines SSTL-2 strong mode in 32M DDR SGRAM which is not supported

in this device.

Figure 4

Extended Mode Register Bitmap

3.3

Signal and Timing Description

3.3.1

The 128Mbit DDR SGRAM is a 16MByte Synchronous Graphics DRAM. It consists of four banks. Each bank is

organized as 4096 rows

×

256 columns

×

32 bits.

Read and Write accesses are burst oriented. Accesses begin with the registration of an Activate command, which

is then followed by a Read or Write command. The address bits registered coincident with the Activate command

are used to select the bank and the row to be accessed. BA1 and BA0 select the bank, address bits A11.. A0 select

the row. Address bits A7.. A0 registered coincident with the Read or Write command are used to select the starting

column location for the burst access.

The regular Single Data Rate SGRAM read and write cycles only use the rising edge of the external clock input.

For the DDR SGRAM, the special signals DQSx (Data Strobe) are used to mark the data valid window. During

General Description

Table 3

A6

IO Driver Strength and Interface Settings

A1

Drive Strength

Strength/

Impedance

60% / 34Ohm

60% / 34Ohm

RFU

30% / 60Ohm

IO Power Supply

VDDQ

2.5V

2.5V

RFU

2.5V

Comment

0

0

1

1

0

1

0

1

SSTL-2 weak

SSTL-2 weak

RFU

matched

impedance mode

replacement for strong mode

–

Do not use

output driver matches line

impedance

DLL

RFU must be set to "0"

A0

0

1

DLL Enable

Enable

Disable

BA1

BA0

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

BA0

0

1

Accessed Register

Extend. Mode Reg.

Extended Mode

Register Access

Mode Register

0

Address Bus

Extended Mode Register

1

DS0

A1

0

1

Drive Strength

A11

A10

DS1

A6

0

0

0

RFU

1

Matched Impedance 2.5V

1

1

RFU must be set to "0"

SSTL II-Weak Mode

SSTL II-Weak Mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB25D128400AT | 128 Mbit Double Data Rate SDRAM |

| HYB25D128400AT-6 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128400ATL-8 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128800AT-6 | 128 Mbit Double Data Rate SDRAM |

| HYB25D128800ATL-8 | 128 Mbit Double Data Rate SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB25D128323C-3.3 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323C-3.6 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323C-4.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323C-5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323CL3.6 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。