- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384402 > HF88M02 (King Billion Electronics Co., Ltd.) 256K x 8 bit Mask ROM PDF資料下載

參數(shù)資料

| 型號(hào): | HF88M02 |

| 廠商: | King Billion Electronics Co., Ltd. |

| 英文描述: | 256K x 8 bit Mask ROM |

| 中文描述: | 256K × 8位掩模ROM |

| 文件頁(yè)數(shù): | 7/19頁(yè) |

| 文件大?。?/td> | 322K |

| 代理商: | HF88M02 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

King Billion Electronics Co., Ltd

駿 億 電 子 股 份 有 限 公 司

HF88M02

January 16, 2004

This specification is subject to change without notice. Please contact sales person for the latest version before use.

Page 7 of 19

V1.11

DIR00

RS = 100 & OEn = '0'

RS = 101 & OEn = '0'

RS = 111 & OEn = '0'

RS = 110 & OEn = '0'

P10

P00

D0

P10

1

0

Q

D

Q

D

P00

DIR00

1

0

Q

D

DIR10

D

Q

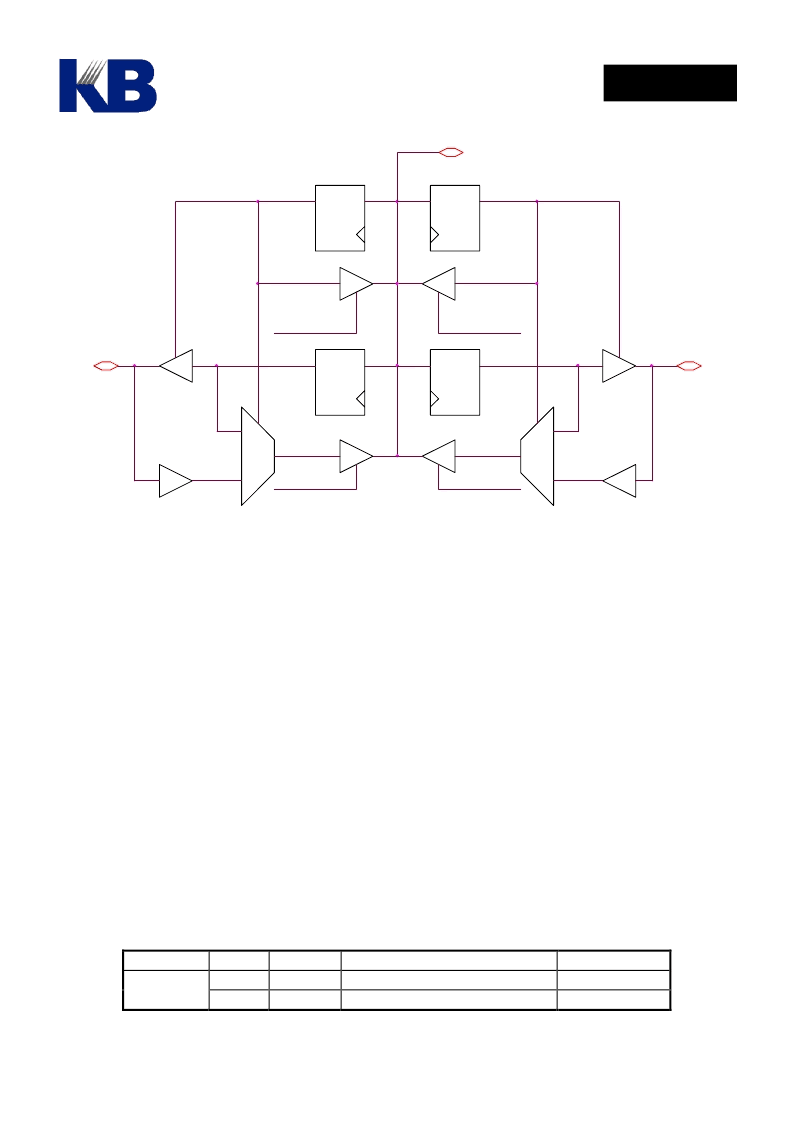

There are seven internal registers used to provide the functionality of Data file as well as Expansion I/O

capability. These registers are selected by RS2 ~ RS0. All registers are 8-bit wide except AC2. AC2

~ AC0 are write-only and constitute the complete 19-bit Address Counter used as pointer to the data.

While the P0, P1, DIR0 and DIR1 can be read as well as written. Their initial values are as indicated in

the following table. When RS2 = ‘0’, the RS1 ~ RS0 are ignored, the Address Counter can be loaded or

contents of Data File can be read. This is to reduce the required pin needed for external MCU to

interface with the Device and also simplify the procedure for loading the address counter.

The P0, P1, DIR0, and DIR1 are used for expansion I/O registers. The P0 and P1 are output registers of

Expansion I/O and DIR0 and DIR1 are the Direction Registers that determine the I/O mode of P0 and P1.

Each pin can be configured as output or input mode individually by setting or resetting the corresponding

pin of the DIR registers. Initially, both P0 and P1 are default to input mode at ‘Hi’ state.

The accesses to the internal registers will be inhibited when CEn is ‘1’. However, the status of internal

registers, such as expansion I/O ports, will not be affected. For example, if a certain pin is in output

mode and driving ‘Hi’, it will not change when CEn pin goes to ‘1’ state. Therefore, the users are

advised to take care of the power down condition of I/O ports when entering sleep mode to prevent

unnecessary power drain.

RS

2

RS

1

RS

0

Symbol

0xx

Type

R

W

Description

Read data by Indirect access

Address latch 2 for A17 ~ A16

Initial Value

“--------“

AC2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HF88M04 | 512K x 8 bit Mask ROM |

| HF88M08 | 512K x 8 bit Mask ROM |

| HF88M32B | command interfaced 4M x 8 bit Mask ROM |

| HF88S05 | command mode SRAM device |

| HFA1105 | 144 MACROCELL 5 VOLT ISP CPLD - NOT RECOMMENDED for NEW DESIGN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HF88M02(S) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HF88M04 | 制造商:KB 制造商全稱:KB 功能描述:512K x 8 bit Mask ROM |

| HF88M04(S) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| HF88M08 | 制造商:KB 制造商全稱:KB 功能描述:512K x 8 bit Mask ROM |

| HF88M08(S) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。