- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371772 > HC05J5GRS 68HC05J5 General Release Specification PDF資料下載

參數(shù)資料

| 型號: | HC05J5GRS |

| 英文描述: | 68HC05J5 General Release Specification |

| 中文描述: | 68HC05J5一般版本規(guī)范 |

| 文件頁數(shù): | 13/106頁 |

| 文件大?。?/td> | 1366K |

| 代理商: | HC05J5GRS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁

July 16, 1999

GENERAL RELEASE SPECIFICATION

MC68HC05J5A

REV 2.1

GENERAL DESCRIPTION

MOTOROLA

1-3

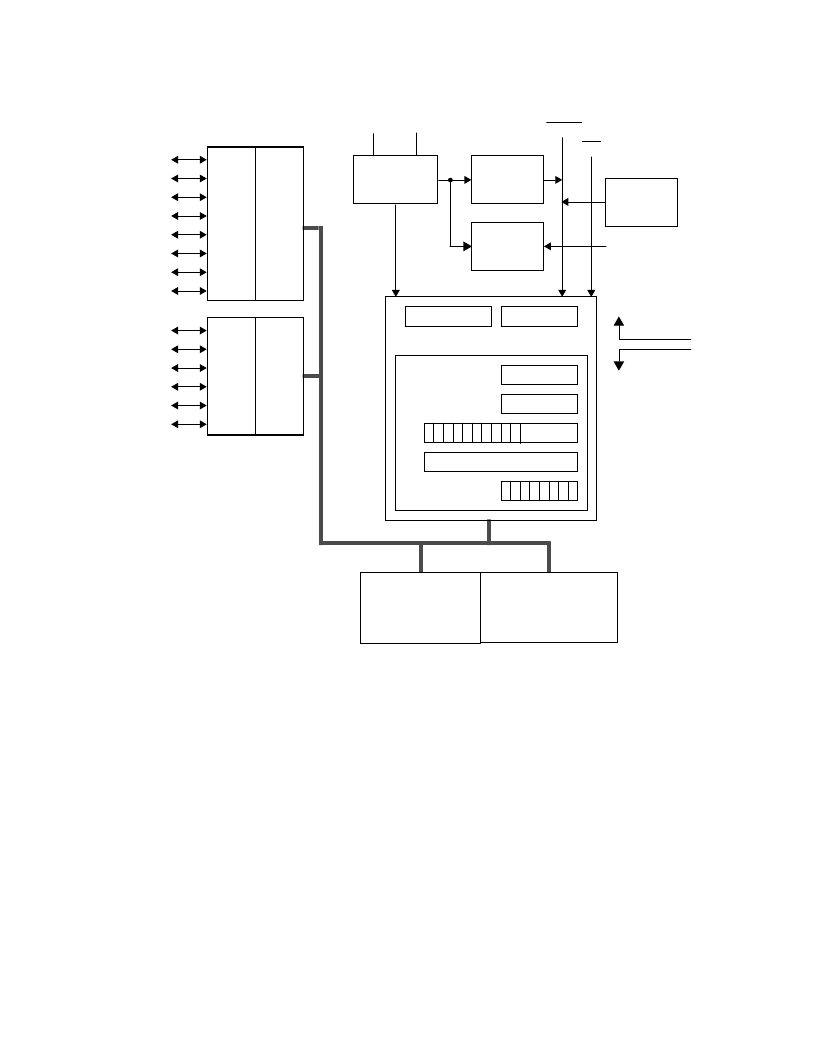

Figure 1-1. MC68HC05J5A Block Diagram

OSCILLATOR

AND DIVIDE

BY 2

OSC1

128 BYTES

RAM

2560 BYTES

ROM

PA0

x

PA1

x

PA2

x

PA3

x

PA4

y

PA5

y

PA6

z

PA7

{

DATA

DIR

REG

PORT

A

REG

IRQ

VDD

VSS

STK PTR

COND CODE REG 1 1 1

I N Z C

H

INDEX REG

CPU CONTROL

0 0 0

1

1

0

0

0

0

0

ALU

68HC05 CPU

ACCUM

PROGRAM COUNTER

CPU REGISERS

OSC2/R

RESET

CORE

TIMER

(COP)

LOW

VOLTAGE

RESET

PB0

|

PB1

}

PB2

}~

PB3

~

PB4

~

PB5

~

DATA

DIR

REG

PORT

B

REG

y

: 8 mA current sink

z

: Open-drained with internal pull-up and

8 mA current sink

{

: External interrupt capability, open-drained

with internal pull-up and 8 mA current sink

|

: Shared pin: PB0/TCAP

}

: 25 mA current sink open-drained with

internal pull-up

x

: External edge interrupt capability

~

: not bonded out in 16-pin package

16-BIT

TIMER

TCAP

|

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HC05JB3GRS | 68HC05JB3 and 68HC705JB3 General Release Specification |

| HC05JB4GRS | 68HC(7)05JB4 General Release Specification |

| HC05JJ6GRS | 68HC05JJ6 and 68HC05JP6 General Release Specification |

| HC05K3GRS | 68HC05K3 General Release Specification |

| HC05PL4GRS | 68HC05PL4A. 68HC05PL4B. 68HC705PL4B General Release Specification |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HC05JB3GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC05JB3 and 68HC705JB3 General Release Specification |

| HC05JB4GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC(7)05JB4 General Release Specification |

| HC05JJ6GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC05JJ6 and 68HC05JP6 General Release Specification |

| HC05K3GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC05K3 General Release Specification |

| HC05PL4GRS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:68HC05PL4A. 68HC05PL4B. 68HC705PL4B General Release Specification |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。