- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄223858 > GMZAN3 (Electronic Theatre Controls, Inc.) XGA ALALOG INTERFACE LCD MONITOR CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | GMZAN3 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | XGA ALALOG INTERFACE LCD MONITOR CONTROLLER |

| 中文描述: | ALALOG的XGA液晶顯示器接口控制器 |

| 文件頁(yè)數(shù): | 5/53頁(yè) |

| 文件大小: | 556K |

| 代理商: | GMZAN3 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

gmZAN3 Preliminary Data Sheet

C0523-DAT-01G

13

July 2003

Ge nes i s Microc hip Confid e n tia l

http:// w ww . g enesis-mic r ochip.com

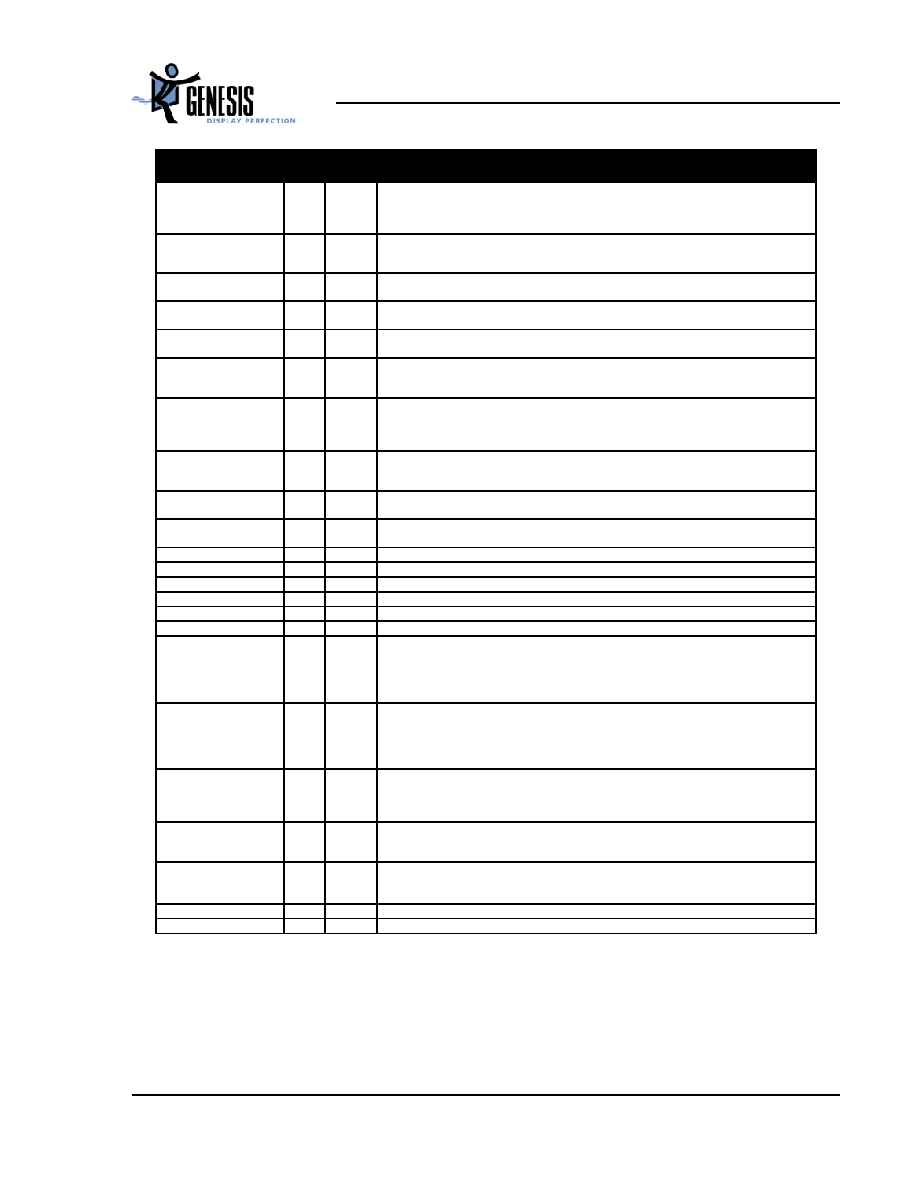

Table 3.

System Interface and GPIO Signals (gmZAN3T)

Pin Name

No

I/O

Description

RESETn

1

IO

Active-low hardware reset signal. The reset signal is held low for at least 150ms on the

chip power up. It has an internal 60Kl pull-up resistor which can be used for re-setting

other system devices. See section 4.2

[Bi-directional (open drain), 5V-tolerant]

RESET_OUT

2

O

Active-high hardware reset signal. The reset signal is held high for at least 150ms on the

chip power up. It can be used for re-setting other system devices[Output, open-drain 5V-

tolerant]

GPIO0/PWM0

80

IO

General-purpose input/output signal or PWM0. Open drain option via register setting.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

GPIO1/PWM1

79

IO

General-purpose input/output signal or PWM1. Open drain option via register setting.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

GPIO2

78

IO

General-purpose input/output signal. Open drain option via register setting.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

GPIO3/IRQn

116

IO

General-purpose input/output signal. This is also active-low interrupt input external micro-

controller.

[Bi-directional, Active low open drain, 5V-tolerant]

GPIO4/MEM_REG

117

IO-PD

General-purpose input/output signal. Open drain option via register setting. For 8-bit A/D

host interface, this selects between OSD memory (high) and register access (low).

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60K pull-

down]

GPIO5/AD7

121

IO

General-purpose input/output signal or Adddress/data[7] for 8-bit A/D host interface. Open

drain option via register setting.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

GPIO6/AD6

122

IO

General-purpose input/output signal or Adddress/data[6] for 8-bit A/D host interface.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

GPIO7/AD5

123

IO

General-purpose input/output signal or Adddress/data[5] for 8-bit A/D host interface.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

GPO8/PD40/OB0

60

O

General-purpose output signal. GPO or TTL 48-bit panel data/Odd Blue0.

GPO9/PD41/OB1

63

O

General-purpose output signal. GPO or TTL 48-bit panel data/Odd Blue1.

GPO10/PD32/OG0

52

O

General-purpose output signal. GPO or TTL 48-bit panel data/Odd Green0.

GPO11/PD33/OG1

53

O

General-purpose output signal. GPO or TTL 48-bit panel data/Odd Green1.

GPO12/PD24/OR0

40

O

General-purpose output signal. GPO or TTL 48-bit panel data/Odd Red0.

GPO13/PD25/OR1

43

O

General-purpose output signal. GPO or TTL 48-bit panel data/Odd Red1.

HDATA0/ADO/HP0

HDATA1/AD1/HP1

128

127

IO-PD

Host data for 6-wire serial protocol.

For 8-bit A/D host interface determines A/D0 and A/D1 bit.

Note: See Table 19, Boostrap Signals

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60K pull-

down]

HDATA2/AD2/OSC_SEL

126

IO-PD

If using 6-wire protocol the HDATA[2] determines bit 2 of the host data. For 8-bit A/D host

interface determines A/D2 bit.

Note: See Table 19, Boostrap Signals

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60K pull-

down]

HDATA3/AD3

125

IO-PD

If using 6-wire protocol the HDATA[3] determines the upper A/D3 bits of the host data. For

8-bit A/D host interface determines address/data bit.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), 5V-tolerant, internal 60K pull-

down]

HFS/AD4

124

IO

Host Frame Sync. Frames the packet on the serial channel 6-wire interface. For 8-bit A/D host

interface determines A/D4 bit.

[Bi-directional, Schmitt trigger (400mV typical hysteresis), slew rate limited, 5V-tolerant]

HCLK/ALE

118

I

Clock signal input for the 6-wire interface and 2-wire modes.

For 8-bit A/D host interface it becomes the Address Latch Enable.

[Input, Schmitt trigger (400mV typical hysteresis), 5V-tolerant]

WRn

119

I-PU

For 8-bit A/D host interface write strobe input. Internal 60K pull-up.

RDn

120

I-PU

For 8-bit A/D host interface read strobe input. Internal 60K pull-up

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GMZAN3L | XGA ALALOG INTERFACE LCD MONITOR CONTROLLER |

| GMZAN3T | XGA ALALOG INTERFACE LCD MONITOR CONTROLLER |

| GMZJ12CT/R | 12.05 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| GMZJ12C | 12.05 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| GMZJ13B | 12.88 V, 0.5 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GMZAN3L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:XGA ALALOG INTERFACE LCD MONITOR CONTROLLER |

| GMZAN3SL-LF-BD | 制造商:STMicroelectronics 功能描述:VIDEO CHIP- PACKAGE - Trays |

| GMZAN3T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:XGA ALALOG INTERFACE LCD MONITOR CONTROLLER |

| GMZJ | 制造商:RECTRON 制造商全稱:Rectron Semiconductor 功能描述:Micro MELF ZENER DIODE 2.5% 500mW |

| GMZJ10 | 制造商:RECTRON 制造商全稱:Rectron Semiconductor 功能描述:Micro MELF ZENER DIODE 2.5% 500mW |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。