- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370261 > FW804 PHY IEEE 1394A Four-Cable Transceiver/Arbiter Device PDF資料下載

參數(shù)資料

| 型號: | FW804 |

| 英文描述: | PHY IEEE 1394A Four-Cable Transceiver/Arbiter Device |

| 中文描述: | PHY的IEEE 1394A端口四線收發(fā)器/仲裁器裝置 |

| 文件頁數(shù): | 20/24頁 |

| 文件大?。?/td> | 398K |

| 代理商: | FW804 |

20

Agere Systems Inc.

Data Sheet, Rev. 3

June 2001

Four-Cable Transceiver/Arbiter Device

FW804 PHY

IEEE

1394A

Internal Register Configuration

(continued)

Table 9. PHY Register Fields for the Cable Environment

(continued)

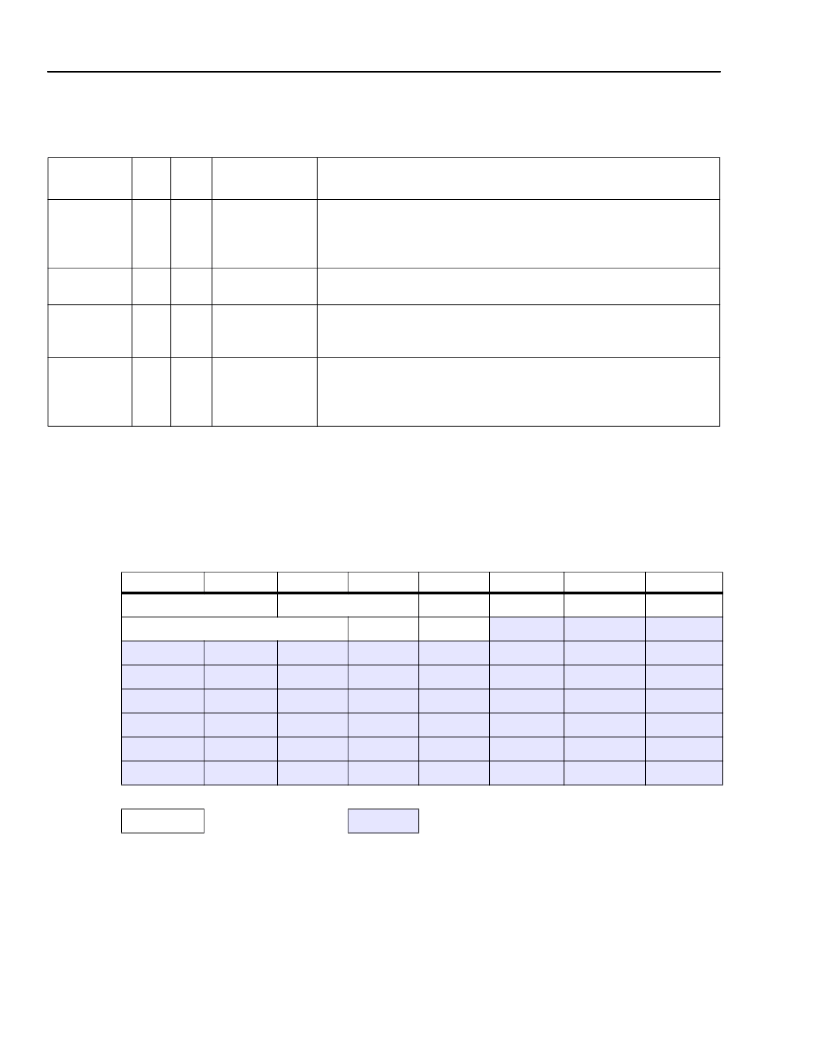

The port status page is used to access configuration and status information for each of the PHY’s ports. The port is

selected by writing zero to Page_select and the desired port number to Port_select in the PHY register at address

0111

2

. The format of the port status page is illustrated by Table 10 below; reserved fields are shown shaded. The

meanings of the register fields with the port status page are defined by Table 11.

Table 10. PHY Register Page 0: Port Status Page

Field

Size Type

Power Reset

Value

Description

Enab_accel

1

rw

0

Enable Arbitration Acceleration.

When set to one, the PHY will

use the enhancements specified in clause 8.11 of 1394a-2000

specification. PHY behavior is unspecified if the value of

Enab_accel is changed while a bus request is pending.

Enable multispeed packet concatenation. When set to one, the

link will signal the speed of all packets to the PHY.

Selects which of eight possible PHY register pages are accessible

through the window at PHY register addresses 1000

2

through

1111

2

, inclusive.

If the page selected by Page_select presents per-port information,

this field selects which port’s registers are accessible through the

window at PHY register addresses 1000

2

through 1111

2

,

inclusive. Ports are numbered monotonically starting at zero, p0.

Enab_multi

1

rw

0

Page_select

3

rw

000

Port_select

4

rw

000

Address

Contents

Bit 0

Bit 1

Bit 2

Bit 3

Bit 4

Bit 5

Bit 6

Bit 7

1000

2

AStat

BStat

Child

Connected

XXXXX XXXXX

Bias

Disabled

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

1001

2

Negotiated_speed

XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX

XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX

XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX

XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX

XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX

XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX XXXXX

Int_enable

Fault

1010

2

1011

2

1100

2

1101

2

1110

2

1111

2

REQUIRED

XXXXX

RESERVED

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FW80960RP-33 | I/O Controller |

| FW82439HX | System Controller |

| FW82443BX | Controller Miscellaneous - Datasheet Reference |

| FW82439TX | Controller Miscellaneous - Datasheet Reference |

| FW82815 | Controller Miscellaneous - Datasheet Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FW804-09-DB | 制造商:AGERE 制造商全稱:AGERE 功能描述:PHY IEEE 1394A Four-Cable Transceiver/Arbiter Device |

| FW808-TL-E | 制造商:SANYO 功能描述:Nch ~ 2 30V 8A 22m@10V 8SOP Tape & Reel 制造商:SANYO Semiconductor Co Ltd 功能描述:MOSFET NN CH 30V 8A SOT96 制造商:Sanyo 功能描述:0 |

| FW80960RP-33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I/O Controller |

| FW80960VH100 | 功能描述:IC MPU I960VH 3V 100MHZ 324-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| FW80960VH100 S L4PH | 制造商:Intel 功能描述:MPU i960? Processor RISC 32-Bit 100MHz 5V 324-Pin BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。