- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370213 > FMS988AKAC100 Signal Conditioner PDF資料下載

參數(shù)資料

| 型號(hào): | FMS988AKAC100 |

| 英文描述: | Signal Conditioner |

| 中文描述: | 信號(hào)調(diào)理 |

| 文件頁(yè)數(shù): | 5/29頁(yè) |

| 文件大小: | 481K |

| 代理商: | FMS988AKAC100 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

FMS9875

PRODUCT SPECIFICATION

REV. 1.2.15 1/14/02

5

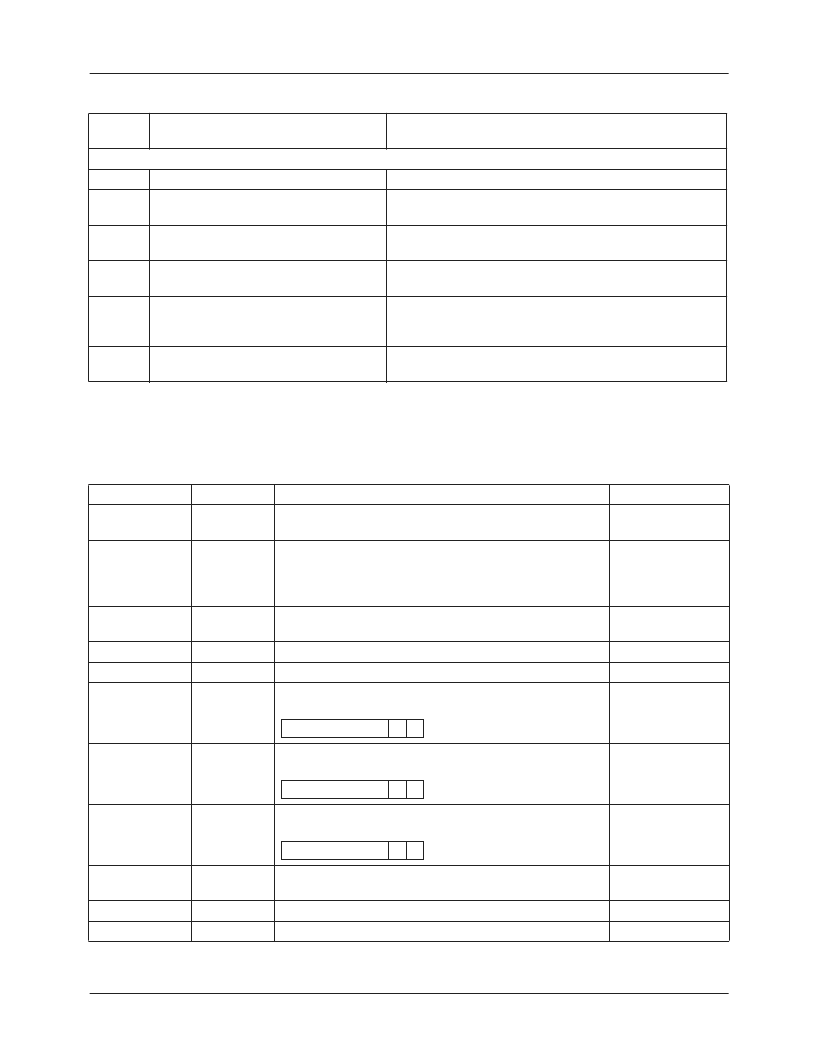

Pin Descriptions

Addressable Memory

Register Map

Pin

Name

Power and Ground

V

DDA

V

DDP

Pin No.

Pin Function Description

5, 7, 11, 13, 17, 19, 95, 99, 100

26, 27, 33, 37, 39

ADC Supply Voltages.

Provide a quiet noise free voltage.

PLL Supply Voltage.

Most sensitive supply voltage.

Provide a very quiet noise free voltage.

Digital Output Supply Voltage.

Decouple judiciously to

avoid propagation of switching noise.

Ground.

Returns for all power supplies. Connect ground

pins to a solid ground-plane.

Voltage Reference Input.

Common reference input to

RGB converters. Connect to VREFOUT, if internal

reference is used.

Voltage Reference Output.

Internal band-gap reference

output. Tie to ground through a 0.1μF capacitor.

V

DDO

50, 60, 62, 72, 85, 91

GND

1, 6, 8, 12, 14, 18, 28, 29, 32, 36, 38, 40,

41, 42, 49, 59, 61, 71, 84, 90, 92, 93, 94

98

V

REFIN

V

REFOUT

97

Name

PLLN

11-4

Address

00

Function

PLL divide ratio, MSBs.

PLLN + 1 = total number of

pixels per horizontal line.

PLL Control Register.

1. Lower four bits of PLL divide ratio.

2. PLL Subdivide phase.

3. PLL Subdivide ratio.

Gain, green/luminance channel.

Adjustable from 70 to

140%.

Gain, blue/P

B

channel.

Adjustable from 70 to 140%.

Gain, red/P

R

channel.

Adjustable from 70 to 140%.

Offset, green/luminance channel.

OSR

5-0

is stored in

the six upper register bits 7-2. Default value is decimal 32.

Default (hex)

69 (1693)

PLLCTRL

01

D0 (1693)

GGY

7-0

02

80

GBP

7-0

GRP

7-0

OSGY

5-0

03

04

05

80

80

80

OSBP

5-0

06

Offset, blue/P

B

channel.

OSR

5-0

is stored in the six

upper register bits 7-2. Default value is decimal 32.

80

OSRP

5-0

07

Offset, red/P

R

channel.

OSR

5-0

is stored in the six upper

register bits 7-2. Default value is decimal 32.

80

CD

7-0

08

Clamp delay.

Delay in pixels from trailing edge of

horizontal sync.

Clamp width.

Width of clamp pulse in pixels.

Configuration Register No. 1

80

CW

7-0

CONFIG 1

09

0A

80

F4

OSGY

5–0

X X

OSBP

5–0

X X

OSRP

5–0

X X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMS988AKAC140 | Signal Conditioner |

| FMU1 | TRANSISTOR | SOT-143R |

| RU101K | TRANSISTOR | SOT-23 |

| FMU3-48R000 | Logic IC |

| FMU3-48R000M | Logic IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMS988AKAC140 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Signal Conditioner |

| FMSA125 | 制造商:MicroSwitch 功能描述:4-DAY SHIPPING -Inductive |

| FMSA-461 | 制造商:INTERPOINT 制造商全稱(chēng):INTERPOINT 功能描述:EMI INPUT FILTER 28 VOLT INPUT |

| FMSA-461/883 | 制造商:INTERPOINT 制造商全稱(chēng):INTERPOINT 功能描述:EMI INPUT FILTER 28 VOLT INPUT |

| FMS-A-C0 | 制造商:Panduit Corp 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。