- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370213 > FMS9875KGC100X 1-Bit Bidirectional Voltage-Level Translator With Auto Direction Sensing and +/-15-kV ESD Protect 6-SOT -40 to 85 PDF資料下載

參數(shù)資料

| 型號(hào): | FMS9875KGC100X |

| 英文描述: | 1-Bit Bidirectional Voltage-Level Translator With Auto Direction Sensing and +/-15-kV ESD Protect 6-SOT -40 to 85 |

| 文件頁(yè)數(shù): | 4/29頁(yè) |

| 文件大小: | 481K |

| 代理商: | FMS9875KGC100X |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

PRODUCT SPECIFICATION

FMS9875

4

REV. 1.2.15 1/14/02

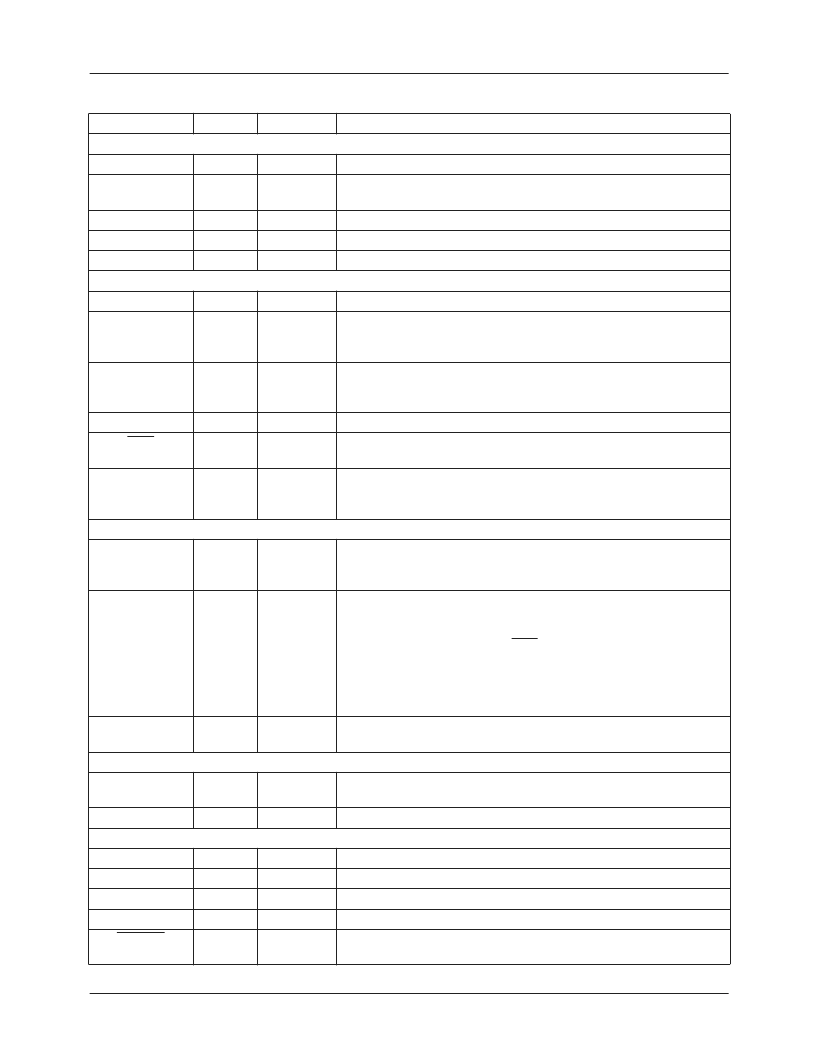

Pin Descriptions

Pin Name

Converter Channels

YG

IN

, BP

IN

YG

REF

, BP

RP

REF

DYG

7-0

DPB

7-0

DPR

7-0

Timing Generator

CLAMP

INVSCK

Pin No.

Type/Value

Pin Function Description

, RP

IN

,

3, 9, 15

4, 10, 16

Input

Input

Analog Inputs.

Clamp Reference Inputs.

RP clamps.

Luminance/Green Channel Data Output.

P

B

/Blue Channel Data Output.

P

R

/Red Channel Data Output.

RGB or YP

B

P

R

.

REF

Voltage reference inputs for YG, BP and

76–83

63–70

51–58

Output

Output

Output

21

20

Input

Input

External Clamp Input.

Invert Sampling Clock.

analog inputs. Supports Alternate Pixel Sampling mode for capture

pixel rates up to 216Ms/s.

External Clock input.

Enabled if register bit, XCKSEL = H.

Replaces PXCK clock generated by PLL. If unused, connect to

ground through a 10k

resistor.

Output Data Clock.

Clock for strobing output data to external logic.

Output Data Clock Inverted.

Inverted clock for strobing output data

to external logic.

Horizontal Sync Output.

Reconstructed HSYNC delayed by

FMS9875 latency with leading edge synchronized to start of data

output. Polarity is always active HIGH.

Inverts SCK, the internal clock sampling the

XCK

34

Input

DCK

DCK

86

87

Output

Output

HSOUT

88

Output

Phase Locked Loop

HSIN

30

Schmitt

Horizontal Sync input.

source should be clamped at 3.3V or current limited, to prevent

overdriving ESD protection diodes.

PLL COAST.

Extraneous or missing horizontal sync pulses can be

ignored by asserting the COAST input. With COAST asserted, the

HSIN signal is ignored by the PLL without affecting PXCK and the

derived clocks: SCK, DCK and DCK. With register bit, COASTPOL = 1:

Schmitt trigger threshold is 1.5V. A 5V

COAST

31

Input

COAST = L: PLL locked to HSIN.

COAST = H: PLL VCO input floats with HSIN disregarded

COAST polarity may be inverted using the COASTPOL register bit.

PLL Low Pass Filter.

Connect recommended PLL filter to LPF pin.

(see

Schematic, PLL Filter

)

LPF

35

Passive

Sync Stripper

ACS

IN

2

Analog Composite Sync Input.

threshold.

Digital Composite Sync Output.

Input to sync stripper with 150mV

DCS

OUT

89

Output from sync stripper.

Control

SDA

SCL

A

A

PWRDN

22

23

24

25

96

Bi-directional

Input

Input

Input

Input

Serial Port Data.

Serial Port Clock.

Address bit 0.

Address bit 1.

Power Down/Output Control.

Powers down the FMS9875 with

outputs high impedance.

Bi-directional data (I

Clock input (I

Lower bit of serial port address.

Upper bit of serial port address.

2

C/SMBUS).

C/SMBUS).

2

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMS9875KGC140 | Integrated Photo Flash Charger and IGBT Driver 16-QFN -35 to 85 |

| FMS9875KGC140X | |

| FMS988AKAC100 | Signal Conditioner |

| FMS988AKAC140 | Signal Conditioner |

| FMU1 | TRANSISTOR | SOT-143R |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMS9875KGC140 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| FMS9875KGC140X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| FMS9875KWC | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| FMS9884A | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:3x8-Bit, 108/140/175 Ms/s Triple Video A/D Converter with Clamps |

| FMS9884AKAC100 | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 MQFP RoHS:否 制造商:Texas Instruments 輸入信號(hào)類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。