- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67428 > FC15A140CC (ATMEL CORP) SPECIALTY ANALOG CIRCUIT, CDIP20 PDF資料下載

參數(shù)資料

| 型號(hào): | FC15A140CC |

| 廠商: | ATMEL CORP |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, CDIP20 |

| 封裝: | 0.300 INCH, CERAMIC, DIP-20 |

| 文件頁數(shù): | 15/16頁 |

| 文件大小: | 382K |

| 代理商: | FC15A140CC |

FC15A140

8/16

Nap mode

The nap mode reduces power consumption when the Finger-

Chip

T is not used. The nap mode is enabled when RESET is

high. At this moment, all flip–flop inside the circuit are posi-

tioned, analog cells do not dissipate power and only bandgap

and circuitry connected to the input clock PCLK consume

power. User may also stop the clock: this is the minimal power

consumption mode.

To summarize, nap mode is when:

– RESET is high

– optionally PCLK is set to low or high

To restart from nap mode, it is recommended this sequence is

followed:

– start the clock PCLK

– set RESET to low.

The TS83148 is a 8 bit/50MSPS low power consumption ADC,

with a nap mode, overflow and underflow signals. See the

TS83148 datasheet for more information.

Image rate and speed of the sweeping

An 8 MHz clock enables the output of 714 images per second:

one image = (30+10)x280=11200 clock pulses

If we assume that we need at least 15 pixels recovery between

two images to reconstruct the complete image, that gives the

maximum speed of the sweeping:

15 x 0.05 x 714 = 535 mm/s or 21 inch/s

that is a very high speed to sweep a finger, and user will prob-

ably not need such a rate.

We recommend to have less than 10 pixels of displacement

between two images (so 20 pixels of recovery between two

images), as 500

mm is roughly the spatial frequency of the

ridges of the fingerprints. A speed of 200 mm/s is already fast,

so that we recommend a clock rate of 4.5 MHz, but this has to

be confirmed:

clock rate = 11200 x sweep speed / (displacement for 1 image).

Conclusion

This is why we propose a two–step approach for development:

first use our evaluation board to adjust the different parameters

to get the best results. Once this is defined, make your final

board that will be drastically simplified compared to the evalua-

tion board.

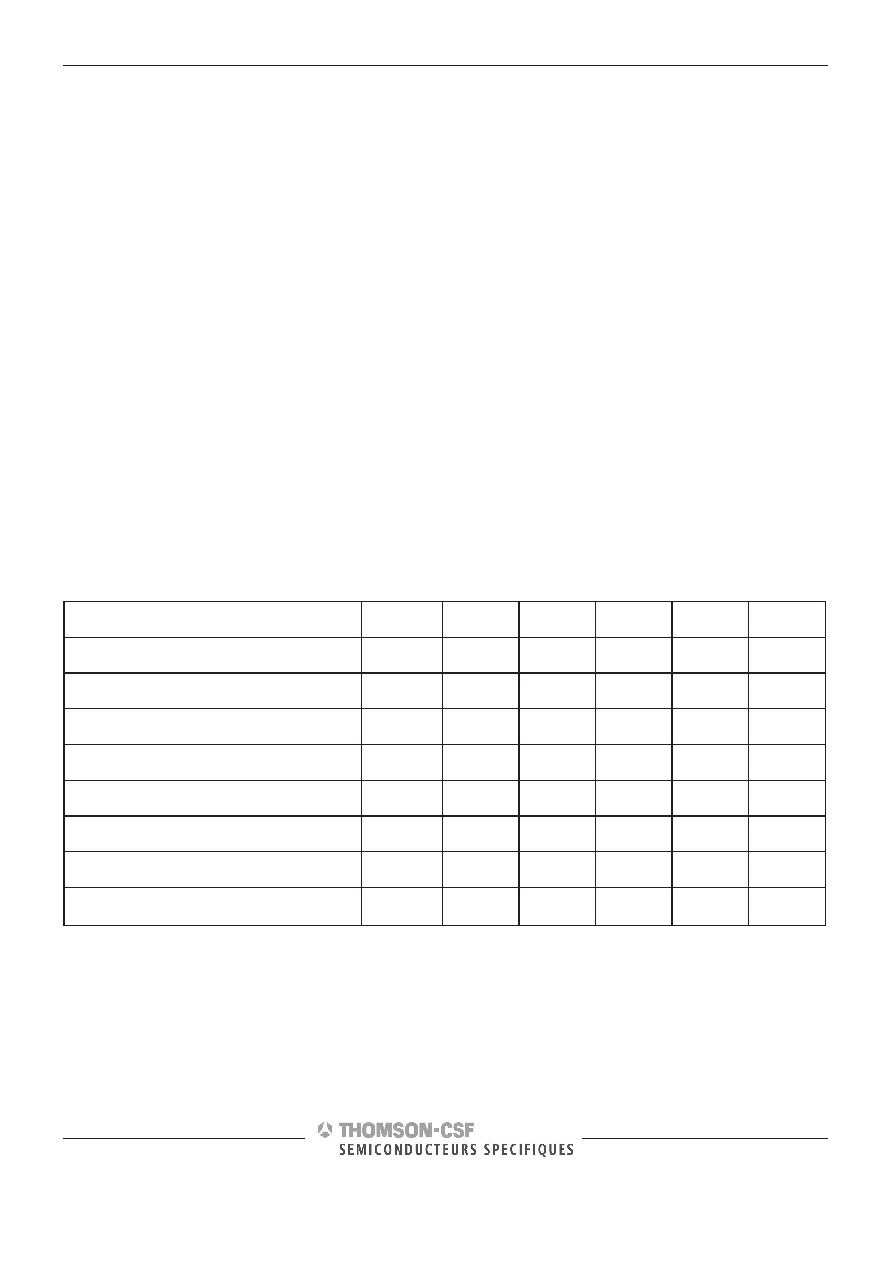

SWITCHING PERFORMANCES

Parameter

Test level

Symbol

Min

Typ

Max

Unit

Clock frequency

FPCLK

0.125

4.0

8.0

MHz

Minimum clock pulse width (high)

TChigh

4000

125

62.5

ns

Minimum clock pulse width (low)

TClow

4000

125

62.5

ns

Setup time of RESET to PCLK

TR setup

0

ns

Output delay from PCLK to SCLK

TPS

44

ns

Output delay from PCLK to LCLK

TPL

40

ns

Output delay from PCLK to FCLK

TPF

45

ns

Aperture of AVIDEO signal for sampling

TAVIDEO

"20

ns

Note

Outputs connected to Cload = 120 pF.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FC15A140CC | SPECIALTY ANALOG CIRCUIT, CDIP20 |

| FC250F | 1-OUTPUT 165 W DC-DC REG PWR SUPPLY MODULE |

| FC250F | 1-OUTPUT 165 W DC-DC REG PWR SUPPLY MODULE |

| FC250C | 1-OUTPUT 250 W DC-DC REG PWR SUPPLY MODULE |

| FC250B | 1-OUTPUT 250 W DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FC-15B-R | 制造商:JAMECO BENCHPRO 功能描述:Test Leads Banana 42 Inches 1 Red 1 Black |

| FC-15H | 制造商:Cinch Connectors 功能描述:15 way IDC snap-together D hood |

| FC15P | 制造商:Cinch Connectors 功能描述:Conn Super Fast D-Sub PIN 15 POS IDT RA Cable Mount 15 Terminal 1 Port 制造商:Cinch Connectors 功能描述:PLUG D IDC 15WAY |

| FC-15P | 制造商:Cinch Connectors 功能描述:Conn Super Fast D-Sub PIN 15 POS IDT RA Cable Mount 15 Terminal 1 Port |

| FC15P0-G1 | 制造商:FCT Group 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。