- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299032 > EP20K400ERI240-1 (ALTERA CORP) LOADABLE PLD, PQFP240 PDF資料下載

參數(shù)資料

| 型號(hào): | EP20K400ERI240-1 |

| 廠商: | ALTERA CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, PQFP240 |

| 封裝: | HEAT SINK, POWER, QFP-240 |

| 文件頁數(shù): | 40/65頁 |

| 文件大?。?/td> | 781K |

| 代理商: | EP20K400ERI240-1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

Altera Corporation

67

Preliminary Information

APEX 20K Programmable Logic Device Family Data Sheet

In designs that require both a multiplied and non-multiplied clock, the

clock trace on the board can be connected to GCLK1. Table 9 shows the

combinations supported by the ClockLock and ClockBoost circuitry. The

GCLK1

pin can feed both the ClockLock and ClockBoost circuitry in the

APEX 20K device. However, when both circuits are used, the other clock

pin (GCLK0) cannot be used.

APEX 20KE ClockLock Feature

APEX 20KE devices include an enhanced ClockLock feature set. These

devices include up to four PLLs, which can be used independently. Two

PLLs are designed for either general-purpose use or LVDS use (on devices

that support LVDS I/O pins). The remaining two PLLs are designed for

general-purpose use. The EP20K200E and smaller devices have two PLLs;

the EP20K300E and larger devices have four PLLs.

The following sections describe some of the features offered by the

APEX 20KE PLLs.

External PLL Feedback

The ClockLock circuit’s output can be driven off-chip to clock other

devices in the system; further, the feedback loop of the PLL can be routed

off-chip. This feature allows the designer to exercise fine control over the

I/O interface between the APEX 20KE device and another high-speed

device, such as SDRAM. When using external feedback, the PLL output

can be multiplied. Also, the clock delay adjustment feature is available.

Clock Multiplication

The APEX 20KE ClockBoost circuit can multiply or divide clocks by a

programmable number. The clock can be multiplied by m/(n

× k), where

m, n, and k range from 1 to 16. Clock multiplication and division can be

used for time-domain multiplexing and other functions, which can reduce

design LE requirements.

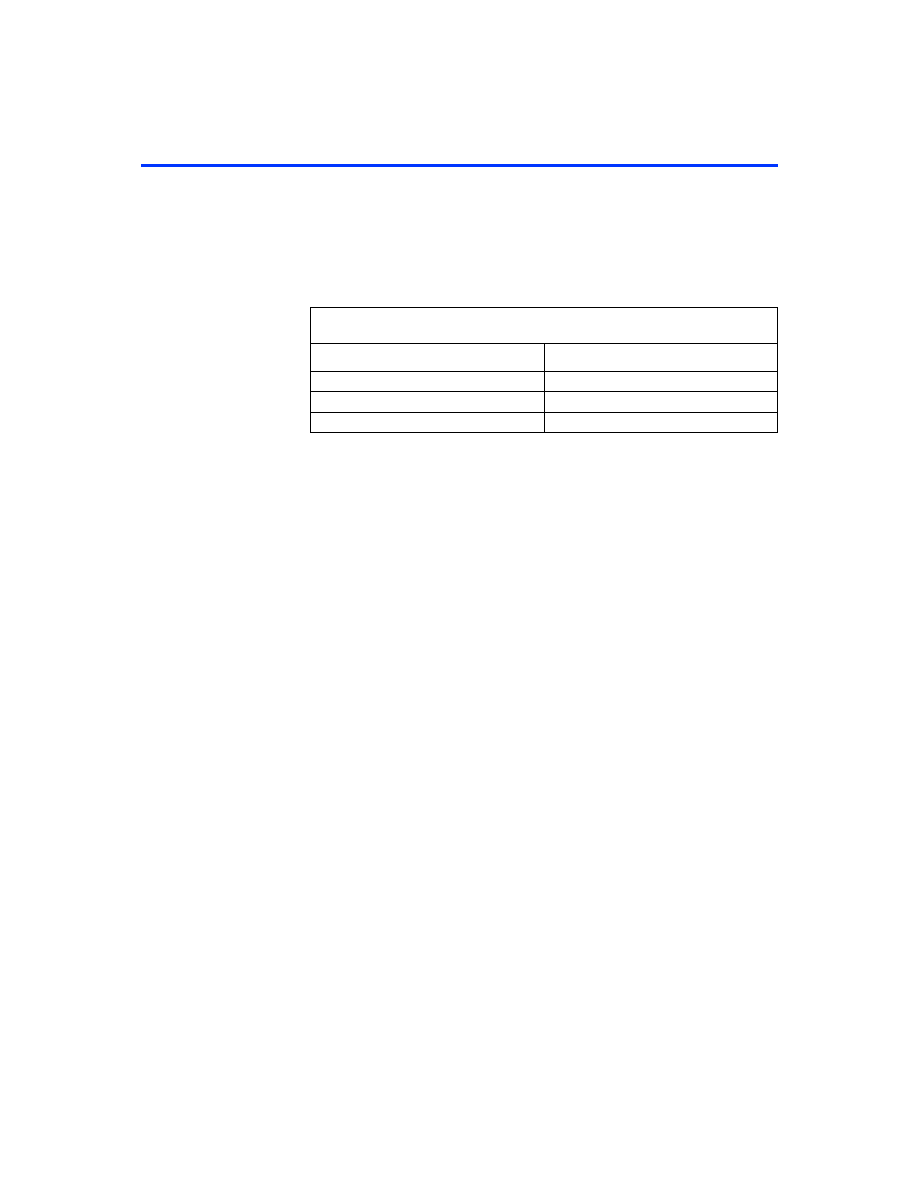

Table 9. Multiplication Factor Combinations

Clock 0

Clock 1

1

×

2

×

1

×

4

×

2

×

4

×

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP20K400ERI240-2 | LOADABLE PLD, PQFP240 |

| EP20K400ERI240-3 | LOADABLE PLD, PQFP240 |

| EP20K400FC672-3X | LOADABLE PLD, 3.6 ns, PBGA672 |

| EPB5065G | 42 MHz, LOW PASS FILTER |

| EPC1000P | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K400FC672-1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-1ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| EP20K400FC672-1X | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-2ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。