- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9752 > DS3252+ (Maxim Integrated Products)IC LIU DS3/E3/STS-1 144-CSBGA PDF資料下載

參數(shù)資料

| 型號: | DS3252+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 16/71頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC LIU DS3/E3/STS-1 144-CSBGA |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 160 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動器/接收器數(shù): | 2/2 |

| 規(guī)程: | IEEE 1149.1 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-BGA,CSPBGA |

| 供應商設備封裝: | 144-TECSBGA(13x13) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

DS3251/DS3252/DS3253/DS3254

23 of 71

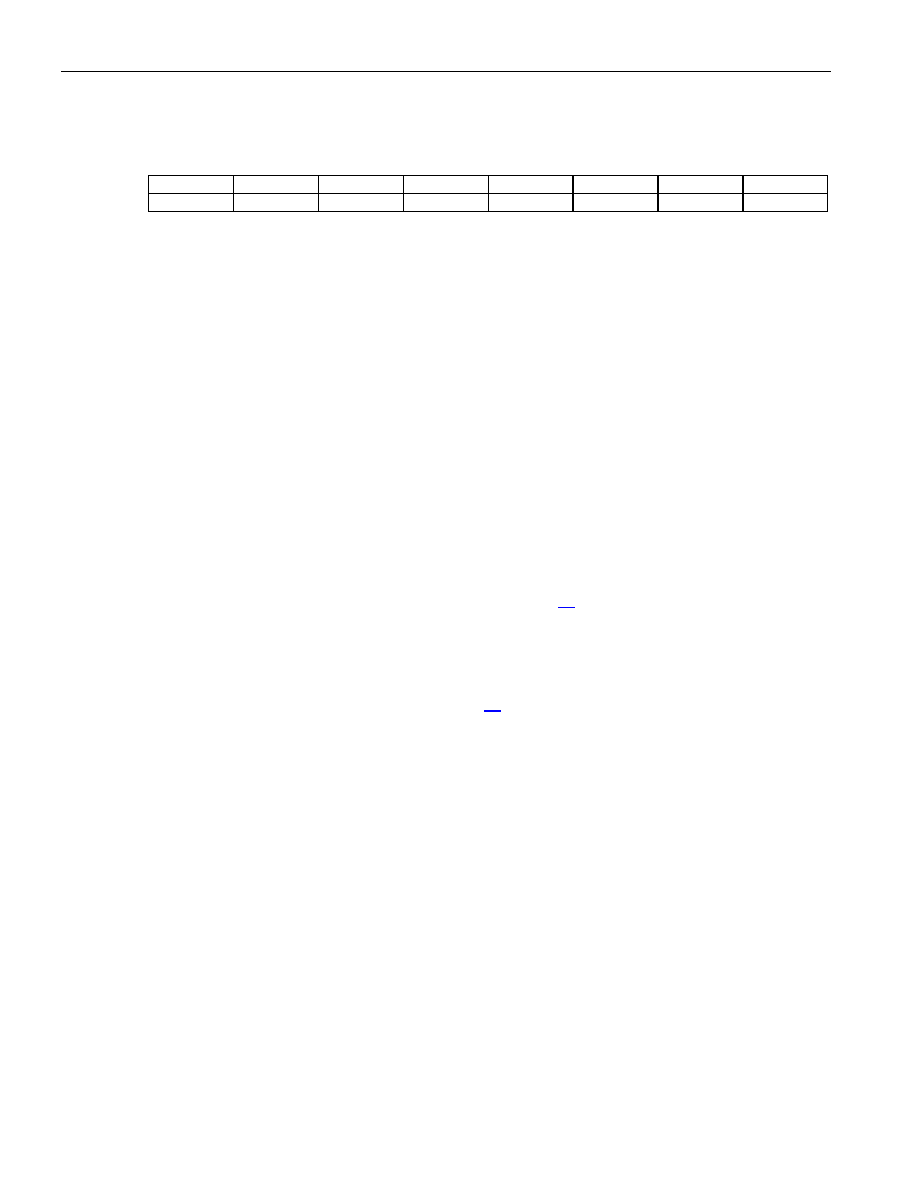

Register Name:

CACR

Register Description:

Clock Adapter Control Register

Register Address:

08h

Bit

7

6

5

4

3

2

1

0

Name

T3MOE

E3MOE

STMOE

—

AMCSEL[1] AMCSEL[0]

AMCEN

Default

0

Bit 7: T3MCLK Output Enable (T3MOE). When the clock adapter block is configured to synthesize the DS3

master clock, the DS3 master clock can be output on the T3MCLK pin by setting T3MOE=1. This clock can then be

used as the transmit clock for neighboring DS3 framers and other components requiring a DS3 clock. This bit

should only be set to 1 if the T3MCLK pin is not driven externally.

0 = T3MCLK output driver disabled

1 = T3MCLK output driver enabled

Bit 6: E3MCLK Output Enable (E3MOE). When the clock adapter block is configured to synthesize the E3 master

clock, the E3 master clock can be output on the E3MCLK pin by setting E3MOE=1. This clock can then be used as

the transmit clock for neighboring E3 framers and other components requiring an E3 clock. This bit should only be

set to 1 if the E3MCLK pin is not driven externally.

0 = E3MCLK output driver disabled

1 = E3MCLK output driver enabled

Bit 5: STMCLK Output Enable (STMOE). When the clock adapter block is configured to synthesize the STS-1

master clock, the STS-1 master clock can be output on the of the STMCLK pin by setting STMOE=1. This clock

can then be used as the transmit clock for neighboring SONET framers, mappers and other components requiring

an STS-1 clock. This bit should only be set to 1 if the STMCLK pin is not driven externally.

0 = STMCLK output driver disabled

1 = STMCLK output driver enabled

Bits 2 to 1: Alternate Master Clock Select (AMCSEL[1:0]). See Section 12 for details.

00 = 19.44 MHz

01 = 38.88 MHz

10 = 77.76 MHz

11 = {unused value}

Bit 0: Alternate Master Clock Enable (AMCEN). See Section 12 for details.

0 = alternate master clock mode disabled

1 = alternate master clock mode enabled

相關PDF資料 |

PDF描述 |

|---|---|

| MAX1230ACEG+ | IC ADC 12BIT 300KSPS 24-QSOP |

| VI-25F-IU-F3 | CONVERTER MOD DC/DC 72V 200W |

| VI-25F-IU-F2 | CONVERTER MOD DC/DC 72V 200W |

| VI-25F-IU-F1 | CONVERTER MOD DC/DC 72V 200W |

| V375C48M150BL2 | CONVERTER MOD DC/DC 48V 150W |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| DS3252+ | 功能描述:網(wǎng)絡控制器與處理器 IC Dual DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3252A3 | 功能描述:網(wǎng)絡控制器與處理器 IC Dual DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3252N | 功能描述:網(wǎng)絡控制器與處理器 IC Dual DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3252N+ | 功能描述:網(wǎng)絡控制器與處理器 IC Dual DS3/E3/STS-1 Line Interface Unit RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3252NA3 | 制造商:Maxim Integrated Products 功能描述:DS3252N REV A3 - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。