- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4567 > DS3184+ (Maxim Integrated Products)IC PACKET PHY W/LIU 400-CSBGA PDF資料下載

參數(shù)資料

| 型號: | DS3184+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 197/400頁 |

| 文件大小: | 0K |

| 描述: | IC PACKET PHY W/LIU 400-CSBGA |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 40 |

| 類型: | 調(diào)幀器 |

| 應(yīng)用: | 數(shù)據(jù)傳輸 |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 400-BBGA |

| 供應(yīng)商設(shè)備封裝: | 400-PBGA(27x27) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁當前第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁第273頁第274頁第275頁第276頁第277頁第278頁第279頁第280頁第281頁第282頁第283頁第284頁第285頁第286頁第287頁第288頁第289頁第290頁第291頁第292頁第293頁第294頁第295頁第296頁第297頁第298頁第299頁第300頁第301頁第302頁第303頁第304頁第305頁第306頁第307頁第308頁第309頁第310頁第311頁第312頁第313頁第314頁第315頁第316頁第317頁第318頁第319頁第320頁第321頁第322頁第323頁第324頁第325頁第326頁第327頁第328頁第329頁第330頁第331頁第332頁第333頁第334頁第335頁第336頁第337頁第338頁第339頁第340頁第341頁第342頁第343頁第344頁第345頁第346頁第347頁第348頁第349頁第350頁第351頁第352頁第353頁第354頁第355頁第356頁第357頁第358頁第359頁第360頁第361頁第362頁第363頁第364頁第365頁第366頁第367頁第368頁第369頁第370頁第371頁第372頁第373頁第374頁第375頁第376頁第377頁第378頁第379頁第380頁第381頁第382頁第383頁第384頁第385頁第386頁第387頁第388頁第389頁第390頁第391頁第392頁第393頁第394頁第395頁第396頁第397頁第398頁第399頁第400頁

DS3181/DS3182/DS3183/DS3184

276

12.10 DS3/E3 Framer

12.10.1 Transmit DS3

The transmit DS3 uses two registers.

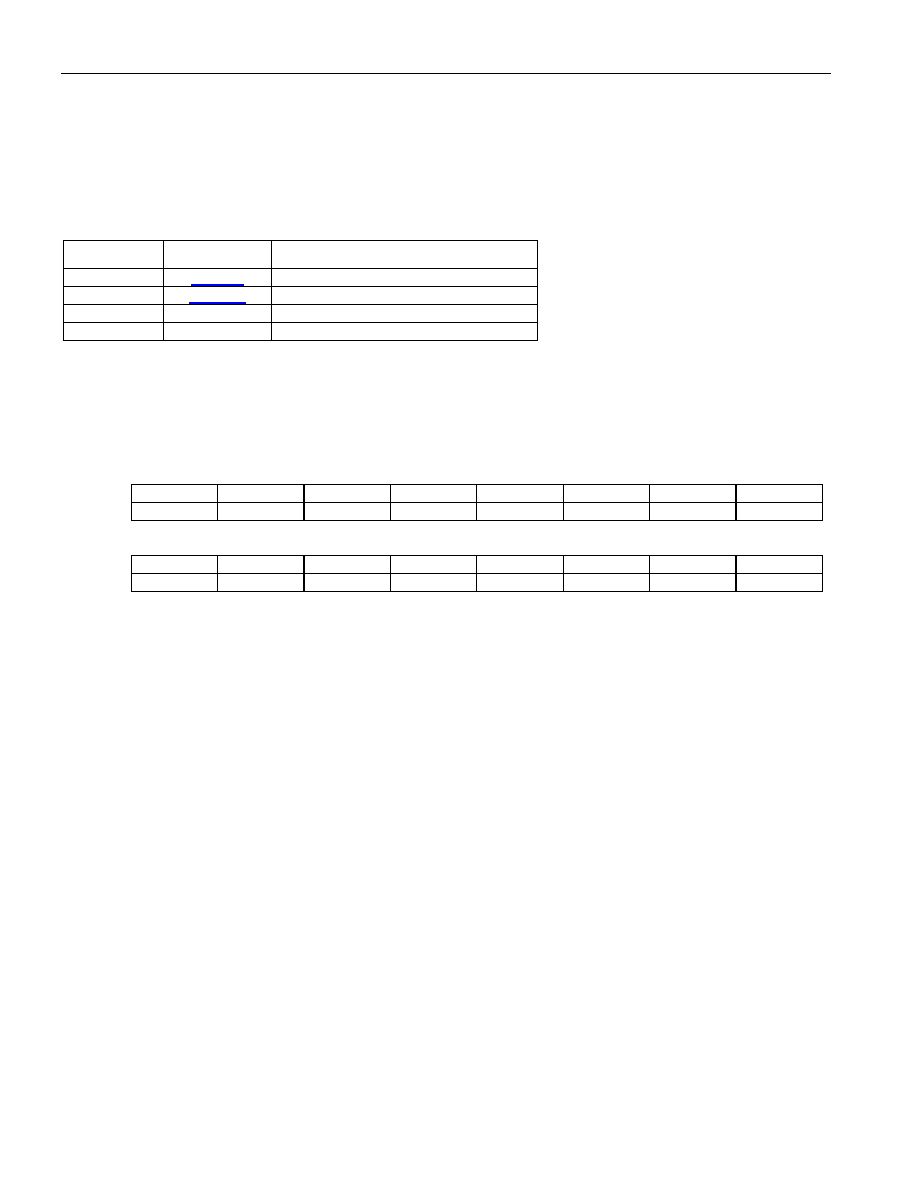

Table 12-33. Transmit DS3 Framer Register Map

ADDRESS

REGISTER

REGISTER DESCRIPTION

(1,3,5,7)18h

T3 Transmit Control Register

(1,3,5,7)1Ah

T3 Transmit Error Insertion Register

(1,3,5,7)1Ch

—

Reserved

(1,3,5,7)1Eh

—

Reserved

12.10.1.1 Register Bit Descriptions

Register Name:

T3.TCR

Register Description:

T3 Transmit Control Register

Register Address:

(1,3,5,7)18h

Bit #

15

14

13

12

11

10

9

8

Name

—

PBGE

TIDLE

CBGD

—

Default

0

Bit #

7

6

5

4

3

2

1

0

Name

—

TFEBE

AFEBED

TRDI

ARDID

TFGC

TAIS

Default

0

Bit 12: P-bit Generation Enable (PBGE) – When 0, Transmit Frame Processor P-bit generation is disabled. If

transmit frame generation is also disabled, the P-bit overhead periods in the incoming DS3 signal will be passed

through to overhead insertion. When 1, Transmit Frame Processor P-bit generation is enabled. The P-bit overhead

periods in the incoming DS3 signal will be overwritten even if transmit frame generation is disabled

Bit 11: Transmit DS3 Idle Signal (TIDLE) –

0 = Transmit DS3 Idle signal is not inserted

1 = Transmit DS3 Idle signal is inserted into the DS3 frame.

Bit 10: C-bit Generation Disable (CBGD) (M23 mode only) – When 0, Transmit Frame Processor C-bit

generation is enabled. The C-bit overhead periods in the incoming M23 DS3 signal will be overwritten with zeros.

When 1, Transmit Frame Processor C-bit generation is disabled. The C-bit overhead periods in the incoming M23

DS3 signal will be treated as payload, and passed through to overhead insertion. This bit is ignored in C-bit DS3

mode. Note: If CBGD = 1, PORT.CR1.NAD must also be set to 1.

Bit 5: Transmit FEBE Error (TFEBE) – When automatic far-end block error generation is defeated (AFEBED = 1),

the inverse of this bit is inserted into the bits C41, C42, and C43. Note: a far-end block error value of zero (TFEBE=1)

indicates a far-end block error. This bit is ignored in M23 DS3 mode.

Bit 4: Automatic FEBE Defeat (AFEBED) – When 0, a far-end block error is automatically generated based upon

the receive parity errors. When 1, a far-end block error is inserted from the register bit TFEBE. This bit is ignored in

M23 DS3 mode.

Bit 3: Transmit RDI Alarm (TRDI) – When automatic RDI generation is defeated (ARDID = 1), the inverse of this

bit is inserted into the X-bits (X1 and X2). Note: an RDI value of zero (TRDI=1) indicates an alarm.

Bit 2: Automatic RDI Defeat (ARDID) – When 0, the RDI is automatically generated based received DS3 alarms.

When 1, the RDI is inserted from the register bit TRDI.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX4507CWN | IC SIGNAL LINE PROTECTOR 18-SOIC |

| MAX4507CAP | IC SIGNAL LINE PROTECTOR 20-SSOP |

| LFXP20C-4F484I | IC FPGA 19.7KLUTS 340I/O 484-BGA |

| MAX4505EUK-T | IC SIGNAL LINE PROTECTOR SOT23-5 |

| LFXP20E-4FN484I | IC FPGA 19.7KLUTS 484FPBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3184+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Quad ATM/Packet PHYs w/Built-In LIU RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3184DK | 功能描述:網(wǎng)絡(luò)開發(fā)工具 RoHS:否 制造商:Rabbit Semiconductor 產(chǎn)品:Development Kits 類型:Ethernet to Wi-Fi Bridges 工具用于評估:RCM6600W 數(shù)據(jù)速率:20 Mbps, 40 Mbps 接口類型:802.11 b/g, Ethernet 工作電源電壓:3.3 V |

| DS3184N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Quad ATM/Packet PHYs w/Built-In LIU RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3184N+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC Quad ATM/Packet PHYs w/Built-In LIU RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS318PIN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Industrial Control IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。